# SN8P2700A 系列

## 用户参考手册

Version 1.1

SN8P2704A SN8P2705A SN8P2706A SN8P2707A SN8P2708A

# SONIX 8 位单片机

SONiX 公司保留对以下所有产品在可靠性,功能和设计方面的改进作进一步说明的权利。SONiX 不承担由本手册所涉及的产品或电路的运用和使用所引起的任何责任,SONiX 的产品不是专门设计来应用于外科植入、生命维持和任何SONiX 产品的故障会对个体造成伤害甚至死亡的领域。如果将 SONiX 的产品应用于上述领域,即使这些是由 SONiX 在产品设计和制造上的疏忽引起的,用户应赔偿所有费用、损失、合理的人身伤害或死亡所直接或间接产生的律师费用,并且用户保证 SONiX 及其雇员、子公司、分支机构和销售商与上述事宜无关。

# 修改记录

| 版本      | 日期     | 说明                          |

|---------|--------|-----------------------------|

| VER 1.0 | 2008.2 | 初版。                         |

| VER 1.0 | 2008.5 | 修改烧录信息章节内容。                 |

| VER 1.1 | 2011.6 | 1、添加 SN8P2704AX SSOP 的封装形式。 |

|         |        | 2、修改 SIO SCK 频率。            |

# 目 录

|   |             |                       | _  |

|---|-------------|-----------------------|----|

| 1 | 产品管         | 5介                    | 6  |

|   | 1.1         |                       |    |

|   | 1.2         | 系统框图                  |    |

|   | 1.3         | 引脚配置                  |    |

|   |             |                       |    |

|   | 1.4         | 引脚说明                  |    |

|   | 1.5         | 引脚电路结构图               |    |

| 2 | 中央処         | b理器(CPU)              | 14 |

|   | 2.1         | 存储器                   | 14 |

|   | 2.1.1       | 程序存储器(ROM)            |    |

|   | 2.1.2       | 编译选项表(CODE OPTION)    |    |

|   | 2.1.2       | 数据存储器(RAM)            |    |

|   |             |                       |    |

|   | 2.1.4       | 系统寄存器                 |    |

|   |             | 寻址模式                  |    |

|   | 2.2.1       | 立即寻址                  |    |

|   | 2.2.2       | 直接寻址                  | 32 |

|   | 2.2.3       | 间接寻址                  | 32 |

|   | 2.3         | 堆栈                    | 33 |

|   | 2.3.1       | 概述                    | 33 |

|   | 2.3.2       | 堆栈寄存器                 |    |

|   | 2.3.3       | 堆栈操作举例                |    |

| 3 |             | <b>华仪</b> 床仆宁 <u></u> |    |

| 9 | 夏型 .<br>3.1 | 概述                    |    |

|   |             |                       |    |

|   | 3.2         | 上电复位                  |    |

|   | 3.3         | 看门狗复位                 |    |

|   | 3.4         | 掉电复位                  | 38 |

|   | 3.4.1       | 概述                    | 38 |

|   | 3.4.2       | 系统工作电压                | 38 |

|   | 3.4.3       | 掉电复位性能改进              |    |

|   |             | 外部复位                  |    |

|   | 3.6         | 外部复位电路                |    |

|   | 3.6.1       | 基本 <b>RC</b> 复位电路     |    |

|   |             |                       |    |

|   | 3.6.2       | 二极管及RC复位电路            |    |

|   | 3.6.3       | 稳压二极管复位电路             |    |

|   | 3.6.4       | 电压偏移复位电路              |    |

|   | 3.6.5       | 外部IC复位                |    |

| 4 | 系统印         | 寸钟                    |    |

|   | 4.1         | 概述                    | 44 |

|   | 4.2         | 系统时钟框图                | 44 |

|   | 4.3         | OSCM寄存器               |    |

|   | 4.4         | 系统高速时钟                |    |

|   | 4.4.1       |                       |    |

|   | 4.4.1       | 系统低速时钟                |    |

|   | _           |                       |    |

| F | 4.5.1       | 系统时钟测试                |    |

| 5 |             | [作模式                  |    |

|   | 5.1         | 概述                    |    |

|   | 5.2         | 系统模式切换                | 50 |

|   | 5.3         | 系统唤醒                  | 51 |

|   | 5.3.1       | 概述                    | 51 |

|   | 5.3.2       | 唤醒时间                  | 51 |

|   | 5.3.3       | P1W唤醒功能控制寄存器          | 51 |

| 6 |             | 1100人在为1011时间11加      |    |

| • | 6.1         | 概述                    |    |

|   | 6.2         |                       | _  |

|   |             | 中断使能寄存器INTEN          |    |

|   | 6.3         | 中断请求寄存器INTRQ          |    |

|   | 6.4         | GIE全局中断               |    |

|   | 6.5         | PUSH,POP处理            |    |

|   | 6.6         | INTO (P0.0) 中断        |    |

|   | 6.7         | INT1 (P0.1) 中断        | 57 |

|   |             |                       |    |

|     | 6.8            | INT2 (P0.2) 中断    |      |

|-----|----------------|-------------------|------|

|     | 6.9            | TO 中断             |      |

|     |                | TC0 中断            |      |

|     |                | TC1 中断            |      |

|     |                | SIO中断             |      |

|     |                | ADC中断             |      |

| 7   | 6.14           | 多中断操作举例           |      |

| 1/  |                |                   |      |

|     |                | VO口上拉电阻           |      |

|     | 7.2            | VO口上拉电阻           |      |

|     |                | VO海极开路寄存器         |      |

|     |                | P4 与ADC共用引脚       |      |

| 8   | -              | B                 |      |

| •   | 8.1            | 看门狗定时器            |      |

|     | 8.2            | 定时器T0             |      |

|     | 8.2.1          | 概述                |      |

|     | 8.2.2          | TOM模式寄存器          |      |

|     | 8.2.3          | TOC计数寄存器          |      |

|     | 8.2.4          | TO 操作流程           |      |

|     | 8.2.5          | T0 定时器的注意事项       | .72  |

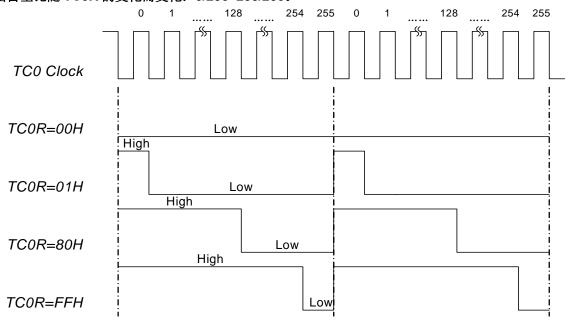

|     | 8.3            | 定时/计数器TC0         | . 73 |

|     | 8.3.1          | 概述                | . 73 |

|     | 8.3.2          | TC0M模式寄存器         | . 74 |

|     | 8.3.3          | TC0C计数寄存器         | . 75 |

|     | 8.3.4          | TC0R自动装载寄存器       |      |

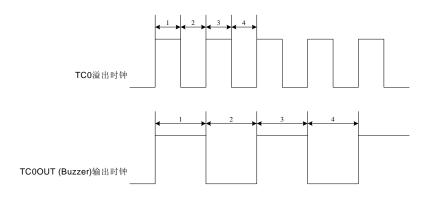

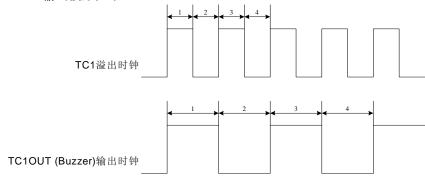

|     | 8.3.5          | TC0 时钟频率输出(蜂鸣器输出) |      |

|     | 8.3.6          | TC0 定时器操作流程       |      |

|     | 8.3.7          | TC0 定时器注意事项       |      |

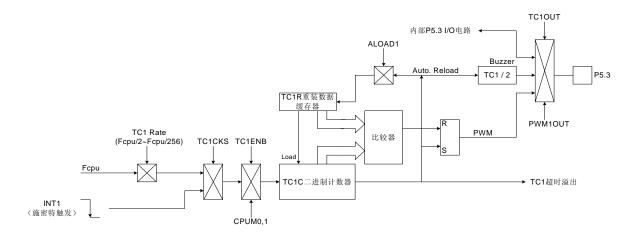

|     | 8.4            | 定时/计数器TC1         |      |

|     | 8.4.1          | 概述                |      |

|     | 8.4.2          | TC1M模式寄存器         |      |

|     | 8.4.3          | TC1C计数寄存器         |      |

|     | 8.4.4          | TC1R自动装载寄存器       |      |

|     | 8.4.5          | TC1 时钟频率输出(蜂鸣器输出) |      |

|     | 8.4.6<br>8.4.7 | TC1 操作流程          |      |

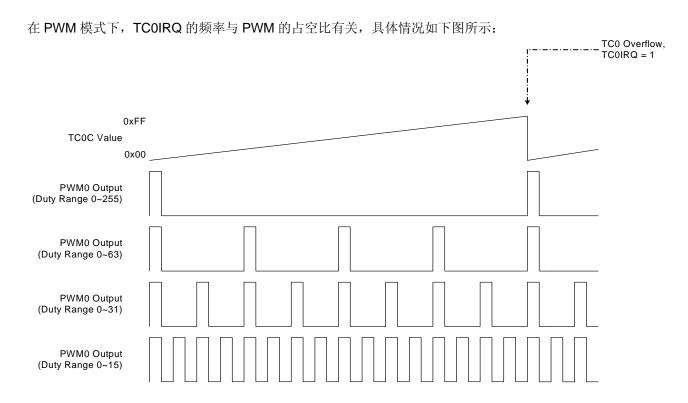

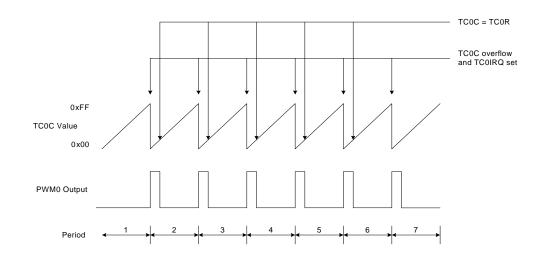

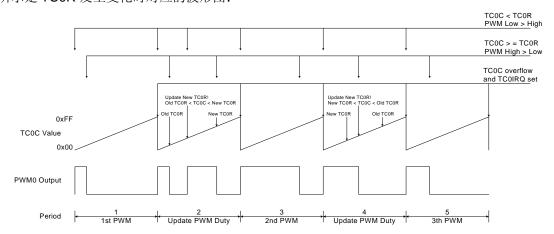

|     | _              | PWM0 模式           |      |

|     |                | 概述                |      |

|     | 8.5.2          | TC0IRQ和PWM0 输出占空比 |      |

|     | 8.5.3          | PWM0 编程举例         |      |

|     | 8.5.4          | PWM0 占空比注意事项      |      |

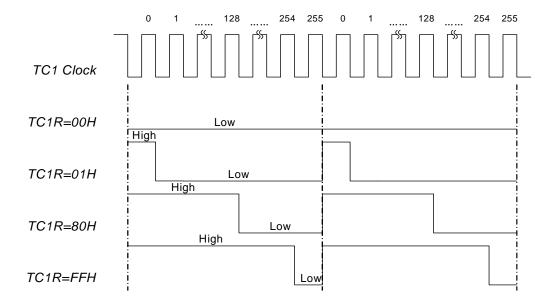

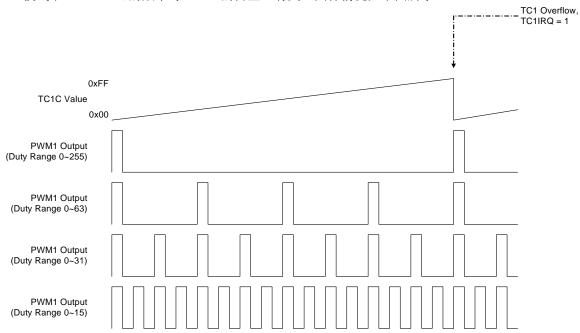

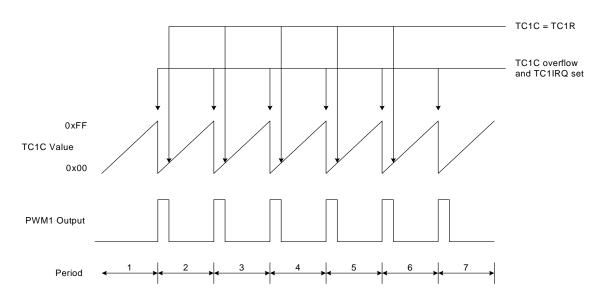

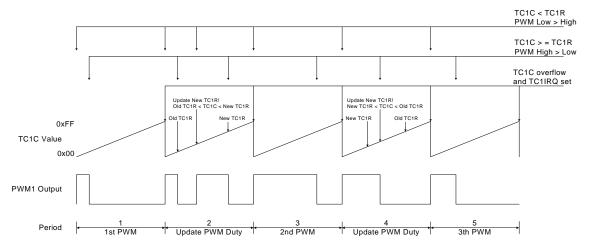

|     |                | PWM1 模式           |      |

|     | 8.6.1          | 概述                |      |

|     | 8.6.2          | <br>TC1IRQ和PWM占空比 | . 92 |

|     | 8.6.3          | PWM1 编程举例         | . 92 |

|     | 8.6.4          | PWM1 占空比注意事项      | . 93 |

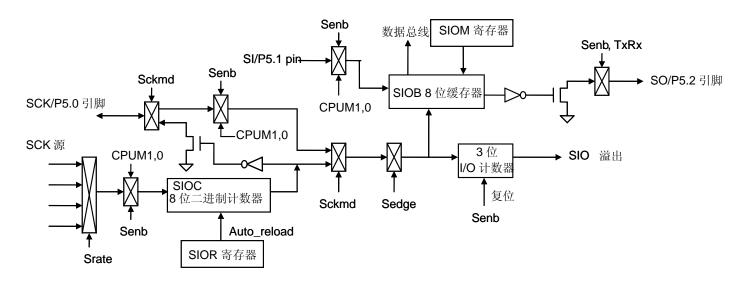

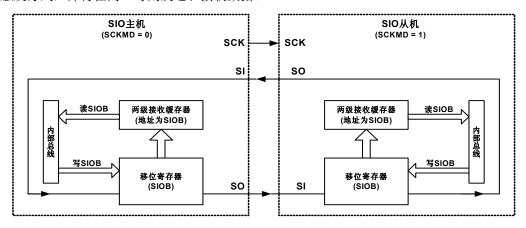

| 9   | 串行业            | 女发器SIO            | . 95 |

|     | 9.1            | 概述                | . 95 |

|     | 9.2            | SIOM模式寄存器         | . 97 |

|     | 9.3            | SIOB数据缓存器         | . 97 |

|     | 9.4            | SIOR寄存器           |      |

| 10  |                | ÎADC              |      |

|     | 10.1           | 概述                |      |

|     |                | ADDR安存器           |      |

|     |                | ADR寄存器            |      |

|     |                | ADB寄存器            |      |

|     |                | P4CON寄存器          |      |

|     | 10.6<br>10.7   | AD <b>转换时间</b>    |      |

|     | 10.7           | ADC电路             |      |

| 11  |                | ADC电时             |      |

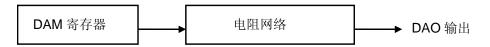

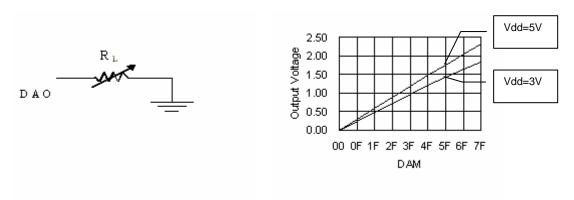

| . 1 | 11.1           | 概述                |      |

|     |                | DAM寄存器            |      |

|     |                |                   |      |

|    | 11.3 D/A | 转换说明                         | 106 |

|----|----------|------------------------------|-----|

| 12 | 指令表      |                              | 107 |

| 13 | 电气特·     | 性                            | 108 |

|    | 13.1 极限  | · 是参数                        | 108 |

|    | 13.2 电气  | <b>(</b> 特性                  | 108 |

|    | 13.3 特性  | - H                          | 109 |

| 14 |          |                              |     |

|    | 14.1 开发  | 之                            | 110 |

|    | 14.1.1   | 在线仿真器(ICE)                   |     |

|    | 14.1.2   | 一次性编程烧录器(OTP烧录器)             |     |

|    | 14.1.3   | 集成开发环境( <b>IDE</b> )         |     |

|    | 14.2 SN8 | 3P2700A的指令限制                 |     |

|    | 14.2.1   | B0MOV M,I                    |     |

|    | 14.2.2   | B0XCH A, M                   | 111 |

|    | 14.3 RO  | M地址 8 处(中断向量)的有效指令           | 112 |

|    | 14.4 SN8 | 3P1708 升级为SN8P2708A          | 113 |

|    | 14.4.1   | 性能比较表                        | 113 |

|    | 14.4.2   | 配置编译选项                       | 114 |

|    | 14.5 SIO | 的移植                          | 115 |

|    | 14.5.1   | SN8P270XA SIO时序图             | 115 |

|    | 14.5.2   | SN8P170X SIO时序图              | 115 |

|    | 14.5.3   | SIOM配置表                      | 116 |

| 15 | OTP烧录作   | 這息                           | 117 |

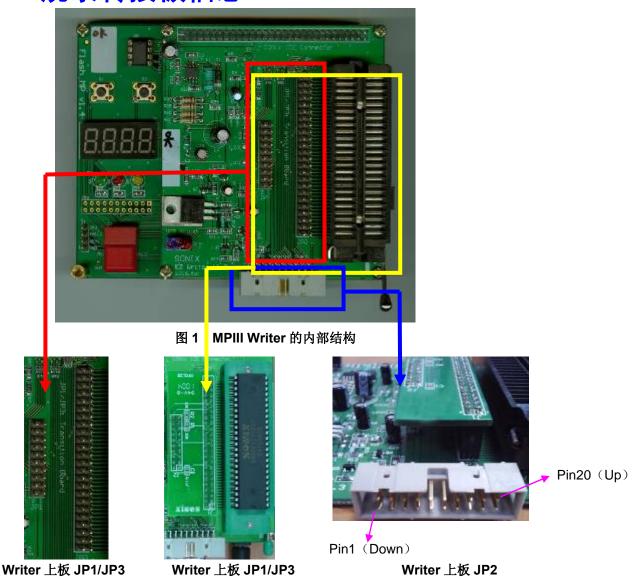

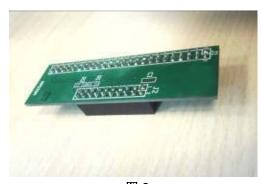

|    | 15.1 烧录  | ·转接板信息                       | 117 |

|    | 15.1.1   | SN8P2700A系列的烧录引脚信息           | 119 |

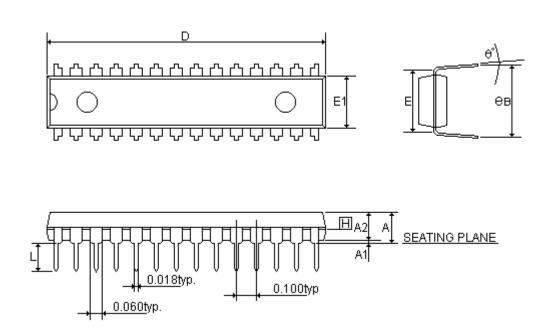

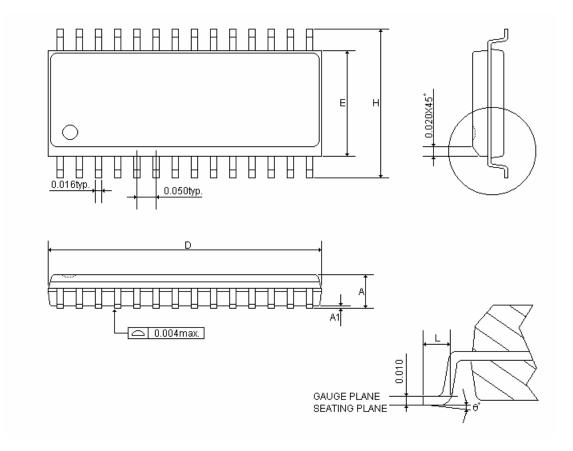

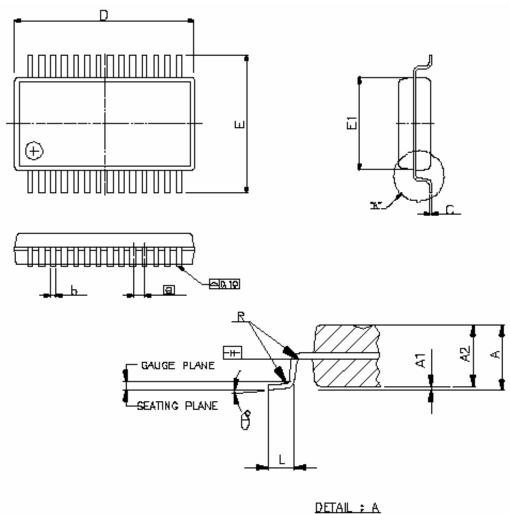

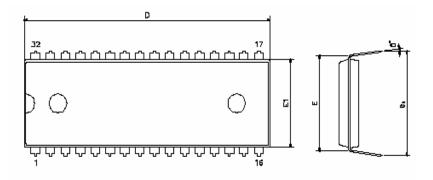

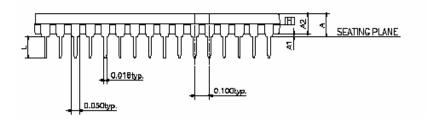

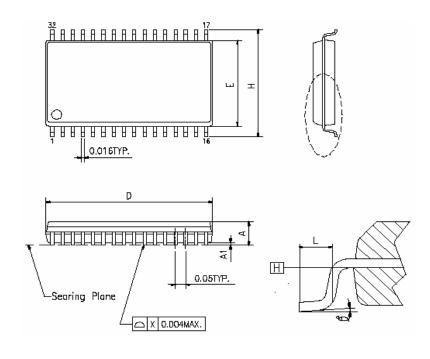

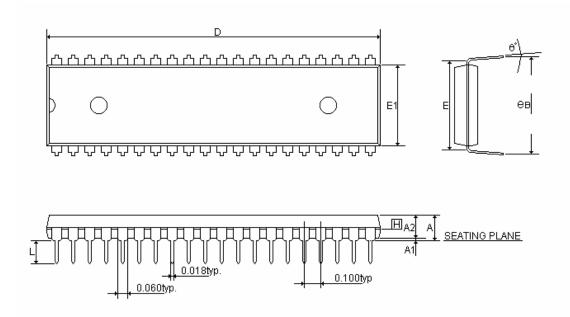

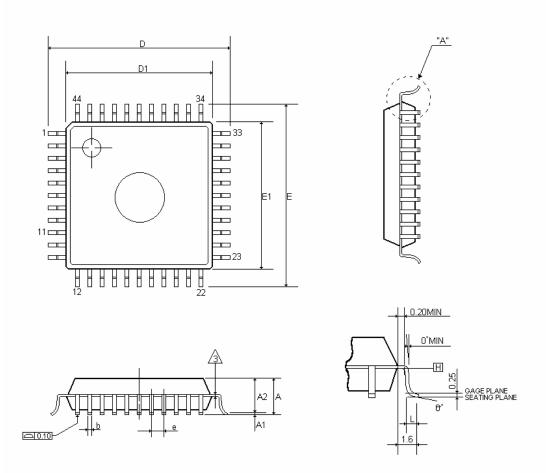

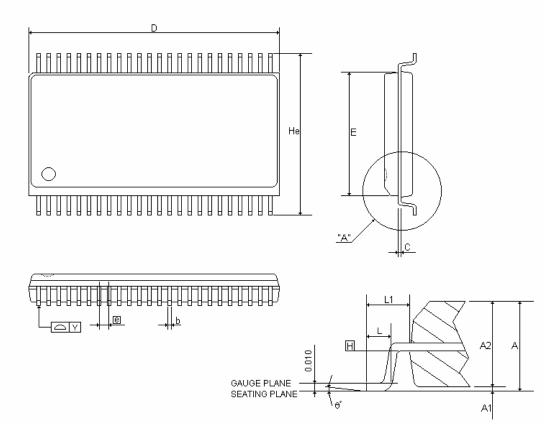

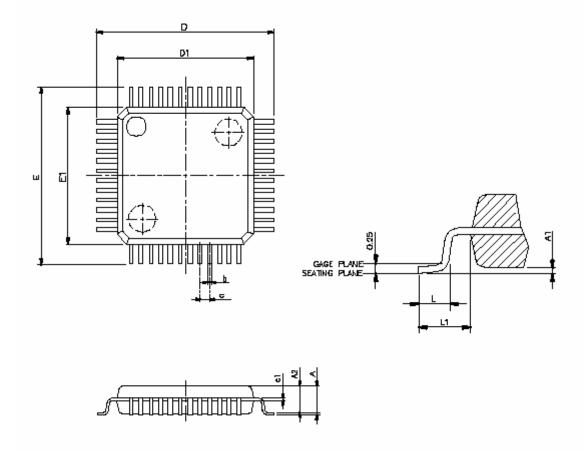

| 16 | 封装       |                              | 120 |

|    |          | DIP28 PIN                    |     |

|    |          | P28 PIN                      |     |

|    |          | DP 28 PIN                    |     |

|    | -        | IP 32 PIN                    | _   |

|    |          | <sup>2</sup> 32 PINIP 40 PIN |     |

|    |          | P 44 PIN                     |     |

|    |          | DP 48 PIN                    |     |

|    |          | FP 48 PIN                    | _   |

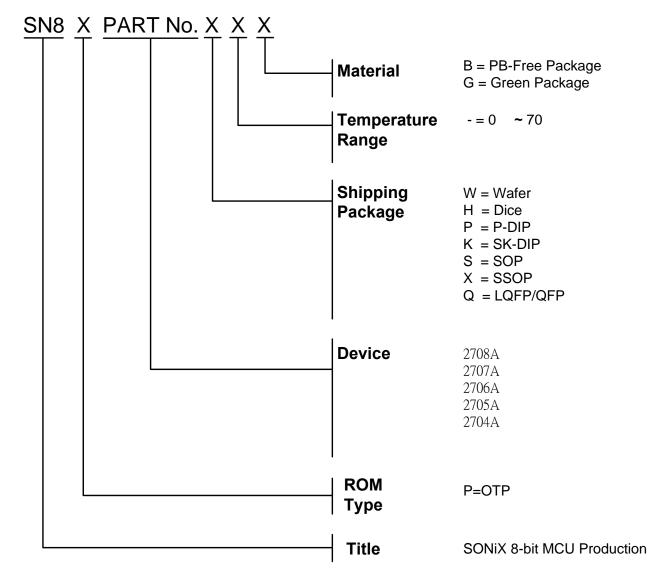

| 17 |          | 正印命名规则                       |     |

|    |          | 2                            |     |

|    |          | - 加型号说明                      |     |

|    | , , ,    | 3举例                          |     |

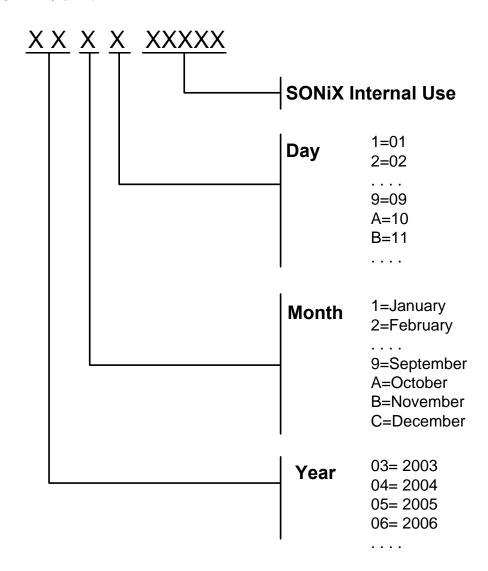

|    |          | 时码规则                         |     |

|    |          |                              |     |

# **1** 产品简介

## 1.1 功能特性

◆ 存储器配置

OTP ROM 空间: 4K \* 16 位。 RAM 空间: 256 字节(bank 0 和 bank 1)。 8 层堆栈缓存器。

◆ I/O 引脚配置 (共 36 个)

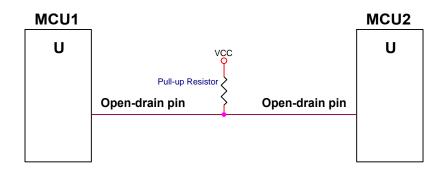

输入输出双向端口: P0、P1、P2、P3、P4、P5。可编程的漏极开路引脚: P1.0、P1.1、P5.2。 具有唤醒功能的端口: P0、P1 的电平变化触发。 外部中断引脚: P0。 内置上拉电阻的端口: P0、P1、P2、P3、P4、P5。 P4 引脚和 ADC 输入引脚共用。

- ◆ 8 通道 12 位 ADC

- ◆ 1通道7位DAC

- ◆ 具有串行通信功能(SIO)

- ◆ 强大的指令系统

单周期指令系统(1T)。 绝大部分指令只需要一个周期。 查表指令 MOVC 可寻址整个 ROM 区。 JMP 和 CALL 指令可寻址整个 ROM 区。 具有硬件乘法器,支持乘法指令(MUL)。 ◆ 8个中断源

5 个内部中断: T0、TC0、TC1、SIO、ADC。 3 个外部中断: INT0、INT1、INT2。

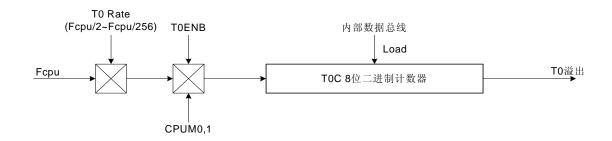

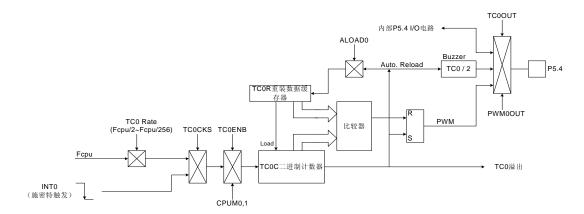

◆ 3个8位定时/计数器

T0: 基本定时器。

TC0: 自动装载定时/计数器/PWM0/Buzzer 输出。 TC1: 自动装载定时/计数器/PWM1/Buzzer 输出。

内置看门狗定时器,时钟源由内部低速 RC 振荡电路提供 (16KHz @3V, 32KHz @5V)

◆ 双时钟系统

外部高速时钟: RC 模式高达 10 MHz。 外部高速时钟: 晶振模式高达 16MHz。

内部低速时钟: RC 模式, 16KHz(3V)、32KHz(5V)。

◆ 工作模式

普通模式: 高、低速时钟同时工作。 低速模式: 只有低速时钟在工作。 睡眠模式: 高、低速时钟同时停止工作。

绿色模式:由 TO 周期性的唤醒。

◆ 封装形式

SN8P2708A: SIP 48pins, SSOP 48 pins, LQFP 48 pins.

SN8P2707A: QFP 44 pins。 SN8P2706A: PDIP 40 pins。

SN8P2705A: PDIP 32 pins, SOP 32 pins.

SN8P2704A: SK-DIP28pins, SOP28pins, SSOP28pins

#### ☞ 特性选择列表

| 单片机型号     | ROM   | RAM   | 推糕 | 定时器 |     | 器 | 1/0 / | ADC | C DAC | PWM    | SIO | 唤醒功能的引脚数目     | 封装形式                 |  |

|-----------|-------|-------|----|-----|-----|---|-------|-----|-------|--------|-----|---------------|----------------------|--|

| 平月が1至 ラ   | KOW   | IVAIN | 产化 | T0  | TC0 |   |       | 700 | סאם   | Buzzer | OIO | 大胜为 配出 刀牌 数 日 | 34/04                |  |

| SN8P2708A | 4K*16 | 256   | 8  | ٧   | V   | ٧ | 36    | 8ch | 1ch   | 2      | 1   | 11            | DIP48/SSOP48/LQFP48  |  |

| SN8P2707A | 4K*16 | 256   | 8  | ٧   | V   | ٧ | 33    | 8ch | 1ch   | 2      | 1   | 9             | QFP44                |  |

| SN8P2706A | 4K*16 | 256   | 8  | ٧   | ٧   | ٧ | 30    | 8ch | 1ch   | 2      | 1   | 9             | DIP40                |  |

| SN8P2705A | 4K*16 | 256   | 8  | ٧   | V   | V | 23    | 8ch | 1ch   | 2      | 1   | 9             | DIP32/SOP32          |  |

| SN8P2704A | 4K*16 | 256   | 8  | ٧   | V   | V | 18    | 5ch | 1ch   | 2      | 1   | 8             | SKDIP28/SOP28/SSOP28 |  |

## ☞ SN8P1700 系列与 SN8P2700A 系列性能比较表

| 项目                                            | SN8P270xA                                                                      | SN8P170x                             |  |

|-----------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|--|

| AC 抗干扰性                                       | 很好(在 VDD 和 VSS 之间添加一个47uf 的旁路电容)                                               | 一般                                   |  |

| 运算速度(16MHz 晶振)                                | 高达 16MIPS                                                                      | 4MIPS                                |  |

| 高速 PWM                                        | PWM 分辨率: 8/6/5/4 位<br>High Clock = 16MHz<br>8 位分辨率时高达 31.25K<br>4 位分辨率时高达 500K | PWM 分辨率: 只 8 位<br>在 16MHz 等于 7.8125K |  |

| 48PIN 封装时最大 I/O 引脚数<br>(SN8P2708A 与 SN8P1708) | 36                                                                             | 33                                   |  |

| 可编程漏极开路输出引脚                                   | P1.0 / P1.1 / P5.2 (SO)                                                        | -                                    |  |

| B0MOV M, I                                    | I 的值不能为 0E6 或 0E7                                                              | 无限制                                  |  |

| B0XCH A, M                                    | M 的地址不能为 80h~FFh                                                               | 无限制                                  |  |

| ROM 中地址 8 处的有效指令                              | JMP 或 NOP                                                                      | 无限制                                  |  |

| ADC 中断                                        | 有                                                                              | -                                    |  |

| ADC VREFL(参考低电压)                              | 有                                                                              | -                                    |  |

| ADC 时钟频率                                      | 七种设置(通过 ADCKS [2:0]设置)                                                         | 两种设置(通过 ADCKS 设置)                    |  |

| 绿色模式                                          | 有                                                                              | -                                    |  |

| 施密特触发输入引脚                                     | 所有的输入引脚(P4 口除外)                                                                | P0、RST、XIN                           |  |

| P0                                            | 输入/输出引脚                                                                        | 输入引脚                                 |  |

| P0.0 中断沿触发                                    | 下降沿/上升沿/双向沿                                                                    | 下降沿                                  |  |

| P0.1/P0.2 中断沿触发                               | 下降沿                                                                            | 下降沿                                  |  |

| P0 和 P1 的唤醒功能                                 | 电平变化触发(下降或上升)                                                                  | 低电平                                  |  |

| 唤醒时间                                          | 1/Fosc*4096 (sec) +振荡器稳定时间                                                     | 1/Fosc*2048 (sec) +振荡器稳定时间           |  |

| SIO 双缓存器                                      | 有                                                                              | -                                    |  |

| SIOM 寄存器的 SEDGE 位的定义                          | 参照 SIO 和使用                                                                     |                                      |  |

| TC0C/TC1C/TC0R/TC1R 的有效范围                     | 00H~ 0FFH                                                                      | 00H ~0FFH                            |  |

| 看门狗计数器时钟源                                     | 内部低速 RC 时钟                                                                     | 外部高速时钟                               |  |

| 看门狗清零                                         | MOV A, #5AH<br>B0MOV WDTR, A                                                   | B0BSET FWDRST                        |  |

| LVD                                           | 1.8V 常开                                                                        | 2.4V ON/OFF                          |  |

| 待机电流                                          | 1uA 5V                                                                         | 9uA 5V(LVD 美闭)                       |  |

#### \* 注:

本手册中提到的电平变化触发是指下降沿触发或上升沿触发;

为避免系统无法进入睡眠模式及降低待机电流,建议用户编程时使能 P1 口未定义引脚相应位的上拉电阻。

SN8P2704A:设置 P1UR的 bit5~bit7为"1"(P1.5~P1.7); SN8P2705A:设置 P1UR的 bit6~bit7为"1"(P1.6~P1.7); SN8P2706A:设置 P1UR的 bit6~bit7为"1"(P1.6~P1.7); SN8P2707A:设置 P1UR的 bit6~bit7为"1"(P1.6~P1.7)。

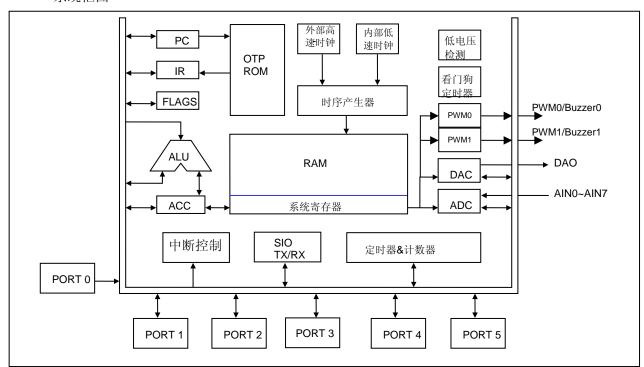

# 1.2 系统框图

系统框图

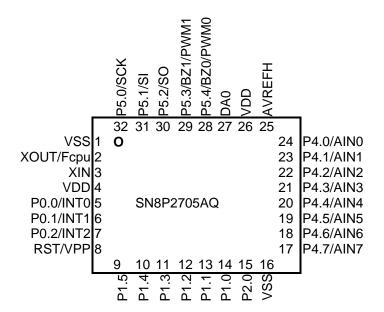

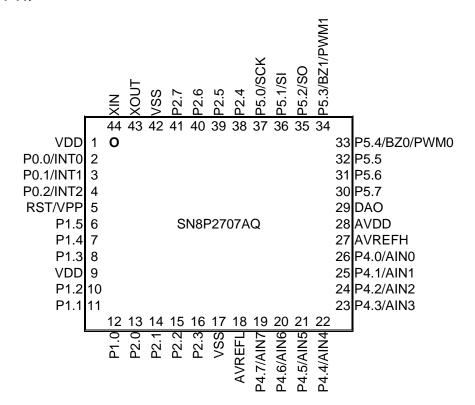

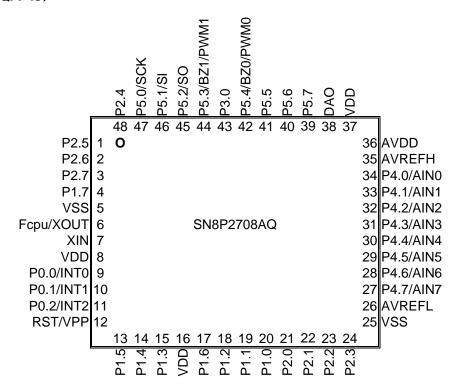

## 1.3 引脚配置

SN8P2704AK (SK-DIP28) SN8P2704AS (SOP28) SN8P2704AX (SSOP28)

|              |    |   |    | 1             |  |  |

|--------------|----|---|----|---------------|--|--|

| P1.4         | 1  | U | 28 | RST/VPP       |  |  |

| P1.3         | 2  |   | 27 | P0.2/INT2     |  |  |

| VDD          | 3  |   | 26 | P0.1/INT1     |  |  |

| P1.2         | 4  |   | 25 | P0.0/INT0     |  |  |

| P1.1         | 5  |   | 24 | VDD           |  |  |

| P1.0         | 6  |   | 23 | XIN           |  |  |

| VSS          | 7  |   | 22 | XOUT          |  |  |

| P4.4/AIN4    | 8  |   | 21 | VSS           |  |  |

| P4.3/AIN3    | 9  |   | 20 | P5.0/SCK      |  |  |

| P4.2/AIN2    | 10 |   | 19 | P5.1/SI       |  |  |

| P4.1/AIN1    | 11 |   | 18 | P5.2/SO       |  |  |

| P4.0/AIN0    | 12 |   | 17 | P5.3/BZ1/PWM1 |  |  |

| AVREFH       | 13 |   | 16 | P5.4/BZ0/PWM0 |  |  |

| VDD          | 14 |   | 15 | DAO           |  |  |

| SN8P2704AK/S |    |   |    |               |  |  |

SN8P2705AP (P-DIP32) SN8P2705AS (SOP32)

| 1            | U                                                                         | 32                                                                             | P5.0/SCK                                                                                                                    |  |  |  |

|--------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2            |                                                                           | 31                                                                             | P5.1/SI                                                                                                                     |  |  |  |

| 3            |                                                                           | 30                                                                             | P5.2/SO                                                                                                                     |  |  |  |

| 4            |                                                                           | 29                                                                             | P5.3/BZ1/PWM1                                                                                                               |  |  |  |

| 5            |                                                                           | 28                                                                             | P5.4/BZ0/PWM0                                                                                                               |  |  |  |

| 6            |                                                                           | 27                                                                             | DAO                                                                                                                         |  |  |  |

| 7            |                                                                           | 26                                                                             | VDD                                                                                                                         |  |  |  |

| 8            |                                                                           | 25                                                                             | AVREFH                                                                                                                      |  |  |  |

| 9            |                                                                           | 24                                                                             | P4.0/AIN0                                                                                                                   |  |  |  |

| 10           |                                                                           | 23                                                                             | P4.1/AIN1                                                                                                                   |  |  |  |

| 11           |                                                                           | 22                                                                             | P4.2/AIN2                                                                                                                   |  |  |  |

| 12           |                                                                           | 21                                                                             | P4.3/AIN3                                                                                                                   |  |  |  |

| 13           |                                                                           | 20                                                                             | P4.4/AIN4                                                                                                                   |  |  |  |

| 14           |                                                                           | 19                                                                             | P4.5/AIN5                                                                                                                   |  |  |  |

| 15           |                                                                           | 18                                                                             | P4.6/AIN6                                                                                                                   |  |  |  |

| 16           |                                                                           | 17                                                                             | P4.7/AIN7                                                                                                                   |  |  |  |

| SN8P2705AP/S |                                                                           |                                                                                |                                                                                                                             |  |  |  |

|              | 3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | 2 31<br>3 30<br>4 29<br>5 28<br>6 27<br>7 26<br>8 25<br>9 24<br>10 23<br>11 22<br>12 21<br>13 20<br>14 19<br>15 18<br>16 17 |  |  |  |

**SN8P2705AQ (LQFP32)**

#### **SN8P2706AP (P-DIP40)**

| _         | ir — |            |    |               |

|-----------|------|------------|----|---------------|

| P1.5      | 1    | U          | 40 | RST/VPP       |

| P1.4      | 2    |            | 39 | P0.2/INT2     |

| P1.3      | 3    |            | 38 | P0.1/INT1     |

| VDD       | 4    |            | 37 | P0.0/INT0     |

| P1.2      | 5    |            | 36 | VDD           |

| P1.1      | 6    |            | 35 | XIN           |

| P1.0      | 7    |            | 34 | XOUT          |

| P2.0      | 8    |            | 33 | VSS           |

| P2.1      | 9    |            | 32 | P2.4          |

| P2.2      | 10   |            | 31 | P5.0/SCK      |

| P2.3      | 11   |            | 30 | P5.1/SI       |

| VSS       | 12   |            | 29 | P5.2/SO       |

| P4.7/AIN7 | 13   |            | 28 | P5.3/BZ1/PWM1 |

| P4.6/AIN6 | 14   |            | 27 | P5.4/BZ0/PWM0 |

| P4.5/AIN5 | 15   |            | 26 | P5.5          |

| P4.4/AIN4 | 16   |            | 25 | P5.6          |

| P4.3/AIN3 | 17   |            | 24 | P5.7          |

| P4.2/AIN2 | 18   |            | 23 | DAO           |

| P4.1/AIN1 | 19   |            | 22 | VDD           |

| P4.0/AIN0 | 20   |            | 21 | AVREFH        |

|           |      | SN8P2706AP |    | •             |

#### **SN8P2707AQ (QFP44)**

#### **SN8P2708AX (SSOP48)**

| P2.5      | 1  | U          | 48 | P2.4          |

|-----------|----|------------|----|---------------|

| P2.6      | 2  |            |    | P5.0/SCK      |

| P2.7      |    |            |    | P5.1/SI       |

| P1.7      | 4  |            | 45 | P5.2/SO       |

| VSS       | 5  |            | 44 | P5.3/BZ1/PWM1 |

| Fcpu/XOUT | 6  |            | 43 | P3.0          |

| XIN       | 7  |            | 42 | P5.4/BZ0/PWM0 |

| VDD       | 8  |            | 41 | P5.5          |

| P0.0/INT0 | 9  |            | 40 | P5.6          |

| P0.1/INT1 | 10 |            | 39 | P5.7          |

| P0.2/INT2 | 11 |            | 38 | DAO           |

| RST/VPP   | 12 |            | 37 | VDD           |

| P1.5      | 13 |            | 36 | AVDD          |

| P1.4      | 14 |            | 35 | AVREFH        |

| P1.3      | 15 |            | 34 | P4.0/AIN0     |

| VDD       | 16 |            | 33 | P4.1/AIN1     |

| P1.6      | 17 |            | 32 | P4.2/AIN2     |

| P1.2      | 18 |            | 31 | P4.3/AIN3     |

| P1.1      | 19 |            | 30 | P4.4/AIN4     |

| P1.0      | 20 |            | 29 | P4.5/AIN5     |

| P2.0      | 21 |            | 28 | P4.6/AIN6     |

| P2.1      |    |            | 27 | P4.7/AIN7     |

| P2.2      |    |            | 26 | AVREFL        |

| P2.3      | 24 |            | 25 | VSS           |

|           |    | SN8P2708AX |    |               |

#### **SN8P2708AQ** (LQFP48)

# 1.4 引脚说明

| 引脚名称                     | 类型   | 功能说明                                                                             |

|--------------------------|------|----------------------------------------------------------------------------------|

| VDD, VSS                 | Р    | 电源输入端。                                                                           |

| AVDD                     | Р    | 模拟电路的电源输入端。                                                                      |

| RST/VPP                  | I, P | RST:系统复位输入引脚,施密特触发,低电平有效,通常保持高电平。<br>VPP:OTP 烧录引脚。                               |

| XIN                      | ı    | 振荡信号输入引脚。                                                                        |

| XOUT/Fcpu                | I/O  | 振荡信号输出引脚。<br>RC 模式时为 Fcpu 的输出引脚。                                                 |

| P0[1:0]/INT[1:0]         | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻,具有唤醒功能。<br>外部中断触发引脚(施密特触发)。<br>TC1/TC0事件计数器的信号输入引脚。 |

| P0.2/INT2                | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻,具有唤醒功能。<br>外部中断触发引脚(施密特触发)。                         |

| P1 [1:0]                 | I/O  | 双向输入/输出引脚,漏极开路引脚,输入模式时为施密特触发,内置上拉电阻。                                             |

| P1 [7:2]                 | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻。                                                    |

| P2 [7:0]                 | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻。                                                    |

| P3.0                     | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻。                                                    |

| P4.[7:0]/AIN[7:0]        | I/O  | 双向输入/输出引脚,非施密特触发,内置上拉电阻。<br>AIN[7:0]: ADC 的输入通道。                                 |

| P5.0/SCK                 | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻。<br>SCK: SIO 时钟引脚。                                  |

| P5.1/SO                  | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻。<br>SO: SIO 数据输出引脚。                                 |

| P5.2/SI                  | I/O  | 双向输入/输出引脚,漏极开路引脚,输入模式时为施密特触发,内置上拉电阻。<br>SI: SIO 数据输入引脚。                          |

| P5[4:3]/BZ[1:0]/PWM[1:0] | I/O  | 双向输入/输出引脚,输入模式时为施密特触发,内置上拉电阻。<br>Buzzer 输出引脚/PWM 输出引脚。                           |

| AVREFH                   | I    | ADC 参考电压的高电平输入引脚。                                                                |

| AVREFL                   | ı    | ADC 参考电压的低电平输入引脚。                                                                |

| DAO                      | 0    | DAC 信号输出引脚。                                                                      |

# 1.5 引脚电路结构图

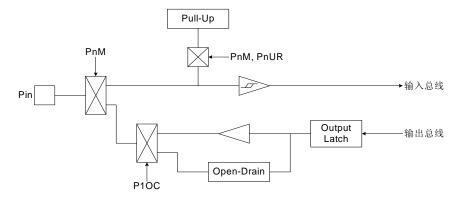

Port 1.0, P1.1, P5.2 结构:

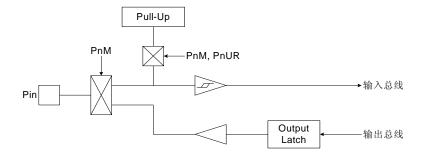

Port 0, 1, 2, 3, 5 结构:

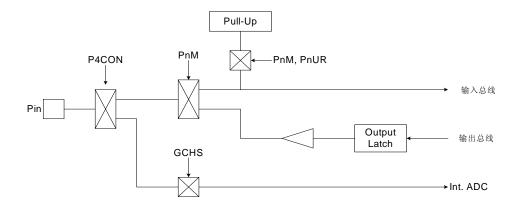

Port 4 结构:

# **2** 中央处理器(CPU)

# 2.1 存储器

## 2.1.1 程序存储器 (ROM)

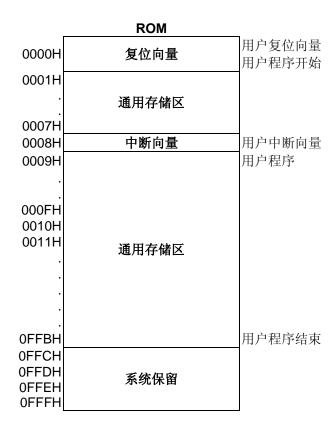

SN8P2700A 的程序存储器为 OTP ROM(一次性可编程),存储器容量为 4K\*16 位,可由 12 位程序计数器 PC 对程序存储器进行寻址,或由系统寄存器(R, X, Y 和 Z) 对 ROM 内的数据进行查表访问。

#### ☞ ROM: 4K

## 2.1.1.1 复位向量(0000H)

具有一个字长的系统复位向量(0000H)。

- 上电复位(NT0=1, NPD=0);

- 看门狗复位(NT0=0, NPD=0);

- 外部复位(NT0=1, NPD=1)。

发生上述任一种复位后,程序将从 0000H 处重新开始执行,系统寄存器也都将恢复为默认值。根据 PFLAG 寄存器中的 NT0 和 NPD 标志位的内容可以判断系统复位方式。下面一段程序演示了如何定义 ROM 中的复位向量。

#### ▶ 例:定义复位向量。

| , CXXIII | ORG<br>JMP | 0<br>START | ;<br>;跳至用户程序。        |

|----------|------------|------------|----------------------|

| START:   | ORG<br>    | 10H        | ;用户程序起始地址。<br>;用户程序。 |

|          | <br>ENDP   |            | ;程序结束。               |

## 2.1.1.2 中断向量(0008H)

中断向量地址为 0008H。一旦有中断响应,程序计数器 PC 的当前值就会存入堆栈缓存器并跳转到 0008H 开始执行中断服务程序。0008H 处的第一条指令必须是"JMP"或"NOP"。下面的示例程序说明了如何编写中断服务程序。

\* 注:"PUSH"、"POP"指令只保存 80H~87H 工作寄存器(包括 PFLAG),响应中断时用户必须通过程序来保存和恢复 ACC。 PUSH/POP 缓存器只有一层,且独立于 RAM 和堆栈区域。

▶ 注:0008H 处的第一条指令必须是"JMP"或者"NOP"。

▶ 例:定义中断向量,中断服务程序紧随 ORG 8 之后。

**ACCBUF**

.DATA

ORG 0 ; 0000H.

DS 1

JMP START ; 跳转到用户程序。

..

ORG 8H ;中断向量。

NOP ; 0008H 处的第一条指令。

BOXCH A, ACCBUF ; 保存 ACC。

PUSH ; 保存 PFLAG 等工作寄存器。

•••

POP ; 恢复 PFLAG 等工作寄存器。

BOXCH A, ACCBUF ; 恢复 ACC。 RETI ; 中断返回。

...

START: ; 用户程序开始。

... ; 用户程序。

JMP START ;

•••

ENDP ;程序结束。

▶ 例:定义中断向量。中断服务程序在用户程序之后。

.DATA ACCBUF DS 1

.CODE

START:

ORG 0 ; 0000H.

JMP START ; 跳转到用户程序。

ORG 8H ;中断向量。

JMP MY\_IRQ ; 0008H, 跳转到中断服务程序。

ORG 10H

; 0010H,用户程序开始。

; 用户程序。

•••

JMP START

MY\_IRQ: ; 中断服务程序开始。

B0XCH A, ACCBUF ; 保存 ACC。

PUSH ; 保存 PFLAG 等工作寄存器。

...

**ENDP**

POP ; 恢复 PFLAG 等工作寄存器。

;程序结束。

BOXCH A, ACCBUF ; 恢复 ACC。 RETI ; 中断返回。

\* 注:从上面的程序中容易得出 SONiX 的编程规则,有以下几点:

1、地址 0000H 的 "JMP"指令使程序从头开始执行;

2、地址 0008H 是中断向量,这里的第一条指令必须是 NOP 或 JMP;

3、用户的程序应该是一个循环。

## 2.1.1.3 查表

在 SONiX 单片机中,对 ROM 区中的数据进行查找,查表指针存放在寄存器 X,Y,Z中。寄存器 X 指向所找数据地 址的高字节(bit16~bit23),寄存器 Y 指向所找数据地址的中间字节(bit8~bit15),寄存器 Z 指向所找数据地址的低字 节(bit0~bit7)。执行完 MOVC 指令后,所查找数据低字节内容被存入 ACC 中,而数据高字节内容被存入 R 寄存器。

注:指令 B0MOV M, I 中的"I" (立即数) 不能是 E7H 或 E6H, 在查表的应用中, 用户必须检查 Y、Z 的值以确保其不为 E6H 或 E7H。设置 ROM 表的地址以避开 E6H 和 E7H。

例: 查找 ROM 地址为 "TABLE1"的值。

**B0MOV** X, #TABLE1\$H ;设置 table1 的高位字节地址。 **B0MOV** Y, #TABLE1\$M ;设置 table1 的中间字节地址。 **B0MOV** Z, #TABLE1\$L ;设置 table1 的低位字节地址。 MOVC ; 查表, R = 00H, ACC = 35H。

; 查找下一地址。

**INCMS** Ζ ; Z+1。 ; Z 没有溢出。 **JMP** @F **INCMS** Υ ; Z 溢出, Y=Y+1。 JMP @F ; Y 没有溢出。 **INCMS** Χ ; Y 溢出, X=X+1。

; 查表, R = 51H, ACC = 05H。

**ORG** 0100H ;设置 TABLE1 的开始地址为 0100H 以避开 "I" (立即数)为 E6H 和 E7H 的

TABLE1: DW 0035H ; 定义数据表数据(16-bit)。

> DW 5105H DW 2012H

NOP

MOVC ...

@@:

注: 当寄存器 Y/Z 溢出(从 FFH 变成 00H)时, X/Y 寄存器并不会自动加 1。用户必须注意这种情况以免查表错误。若 Z 溢出, Y 必须由程序加 1,同样,Y 溢出时,X 也要加 1。下面的宏指令 INC\_XYZ 可以对 X、Y 和 Z 寄存器自动处理。

▶ 例:宏指令INC\_XYZ。

INC\_XYZ **MACRO INCMS** Ζ ; Z+1。

JMP @F ;没有溢出。

**INCMS** Υ ; Y+1。 **JMP** @F ;没有溢出。

**INCMS** Х ; X+1。 NOP ;没有溢出。

@@:

**ENDM**

▶ 例:通过宏指令 INC\_XYZ 对上例优化。

BOMOV X, #TABLE1\$H ; 设置 table1 的高位字节地址。 BOMOV Y, #TABLE1\$M ; 设置 table1 的中间字节地址。 BOMOV Z, #TABLE1\$L ; 设置 table1 的低位字节地址。 MOVC : 香表,R = 00H,ACC = 35H。

INC\_XYZ : 查找下一地址。

@@: MOVC ; 查表, R = 51H, ACC = 05H。

ORG 0100H ; 设置 TABLE1 的开始地址为 0100H 以避开 "I" (立即数)为 E6H 和

E7H 的情况。

TABLE1: DW 0035H ; 定义数据表数据(16-bit)。

DW 5105H DW 2012H

...

...

下面的程序通过累加器对X、Y和Z寄存器进行处理来实现查表功能,但需要特别注意进位时的处理。

▶ 例:通过指令 B0ADD/ADD 实现查表功能。

BOMOVX, #TABLE1\$H; 设置 table1 的高位字节地址。BOMOVY, #TABLE1\$M; 设置 table1 的中间字节地址。BOMOVZ, #TABLE1\$L; 设置 table1 的低位字节地址。

B0MOV A, BUF ;  $Z = Z + BUF_{\circ}$

BOADD Z, A

BOBTS1 FC ; 检查进位标志。

JMP GETDATA ; FC = 0. INCMS Y ; FC = 1, Y+1.

JMP GETDATA ; Y 没有溢出。 INCMS X ; Y 溢出,X=X+1。

NOP

GETDATA: ;

MOVC ; 存储数据, 如果 BUF = 0, 数据为 35H。

;如果BUF = 1,数据=5105H。 ;如果BUF = 2,数据=2012H

...

ORG 0100H ; 设置 TABLE1 的开始地址为 0100H 以避开 "I" (立即数)为 E6H 和 E7H

的情况。

TABLE1: DW 0035H ; 定义数据表数据(16-bit)。

DW 5105H DW 2012H

...

### 2.1.1.4 跳转表

跳转表能够实现多地址跳转功能。由于 PCL 和 ACC 的值相加即可得到新的 PCL,因此,可以通过对 PCL 加上不同 的 ACC 值来实现多地址跳转。ACC 值若为 n,PCL+ACC 即表示当前地址加 n,执行完当前指令后 PCL 值还会自加 1, 可参考以下范例。如果 PCL+ACC 后发生溢出, PCH 则自动加 1。由此得到的新的 PC 值再指向跳转指令列表中新的地 址。这样,用户就可以通过修改 ACC 的值轻松实现多地址的跳转。

注:PCH 只支持 PC 增量运算,而不支持 PC 减量运算。当 PCL+ACC 后如有进位,PCH 的值会自动加 1。PCL-ACC 后若有借 位,PCH 的值将保持不变,用户在设计应用时要加以注意。

#### 例:跳转表。

ORG 0100H ;跳转表从 ROM 前端开始。

**BOADD** PCL, A ; PCL = PCL + ACC, PCL 溢出时 PCH 加 1。 A0POINT

JMP ; ACC = 0, 跳至 A0POINT。 **JMP** A1POINT ; ACC = 1, 跳至 A1POINT。 **A2POINT JMP** ; ACC = 2, 跳至 A2POINT。 **JMP A3POINT** : ACC = 3, 跳至 A3POINT。

SONiX 单片机提供一个宏以保证可靠执行跳转表功能,它会自动检测 ROM 边界并将跳转表移至适当的位置。但采用 该宏程序会占用部分 ROM 空间。

#### 例:如果跳转表跨越 ROM 边界,将引起程序错误。

@JMP\_A **MACRO** VAL

> IF ((\$+1) !& 0XFF00) !!= ((\$+(VAL)) !& 0XFF00)

**JMP** (\$ | 0XFF) ORG (\$ | 0XFF) **ENDIF**

B0ADD PCL, A

**ENDM**

### 注: "VAL"为跳转表列表中列表个数。

#### 例:宏 "MACRO3.H"中, "@JMP\_A"的应用。

**B0MOV** A, BUF0 "BUF0"从0至 4。 @JMP\_A 5 ; 列表个数为 **5**。

**A0POINT** JMP ; ACC = 0, 跳至 A0POINT。 JMP A1POINT ; ACC = 1, 跳至 A1POINT。 **JMP** A2POINT ; ACC = 2, 跳至 A2POINT。 **A3POINT JMP** ; ACC = 3, 跳至 A3POINT。 **JMP** A4POINT

; ACC = 4, 跳至 A4POINT。

如果跳转表恰好位于 ROM BANK 边界处(00FFH~0100H),宏指令"@JMP\_A"将调整跳转表到适当的位置(0100H)。

; ACC = 4,跳至 A4POINT。

## ▶ 例: "@JMP\_A"运用举例。

JMP

;编译前 ROM 地址

|       | B0MOV  | A, BUF0 | ;"BUF0"从 0 到 4。       |

|-------|--------|---------|-----------------------|

|       | @JMP_A | 5       | ;列表个数为5。              |

| 00FDH | JMP    | A0POINT | ; ACC = 0,跳至 A0POINT。 |

| 00FEH | JMP    | A1POINT | ; ACC = 1,跳至 A1POINT。 |

| 00FFH | JMP    | A2POINT | ; ACC = 2,跳至 A2POINT。 |

| 0100H | JMP    | A3POINT | ; ACC = 3,跳至 A3POINT。 |

| 0101H | JMP    | A4POINT | ; ACC = 4,跳至 A4POINT。 |

|       |        |         |                       |

;编译后 ROM 地址

0104H

| B0MOV  | A, BUF0                     | ;"BUF0"从 0 到 4。                              |

|--------|-----------------------------|----------------------------------------------|

| @JMP_A | 5                           | ;列表个数为5。                                     |

| JMP    | A0POINT                     | ; ACC = 0,跳至 A0POINT。                        |

| JMP    | A1POINT                     | ; ACC = 1,跳至 A1POINT。                        |

| JMP    | A2POINT                     | ; ACC = 2,跳至 A2POINT。                        |

| JMP    | A3POINT                     | ; ACC = 3,跳至 A3POINT。                        |

|        | @JMP_A<br>JMP<br>JMP<br>JMP | @JMP_A 5 JMP A0POINT JMP A1POINT JMP A2POINT |

A4POINT

;用户程序结束地址低位地址存入 end\_addr1。

;用户程序结束地址中间地址存入 end\_addr2。

## 2.1.1.5 CHECKSUM计算

ROM 区末端位置的几个字限制使用,进行 Checksum 计算时,用户应避免对该单元的访问。

例:示例程序演示了如何对 00H 到用户程序结束进行 Checksum 计算。

A,#END\_USER\_CODE\$L MOV

**B0MOV** END\_ADDR1, A

A,#END\_USER\_CODE\$M MOV

**B0MOV** END\_ADDR2, A

CLR Υ ; 清 Y。 Ζ CLR ; 清 Z。

@@:

MOVC

ADD

**B0BCLR** FC

DATA1, A

MOV A, R

DATA2, A ADC

**JMP** END\_CHECK ; 检查 YZ 地址是否为代码的结束地址。

AAA:

**INCMS** Ζ

**JMP** @B ;若 Z!= 00H,进行下一个计算。

Y\_ADD\_1 **JMP** ; 若 Z = 00H, Y+1。

END\_CHECK:

MOV A, END\_ADDR1

**CMPRS** A, Z

; 检查 Z 地址是否为用户程序结束地址低位地址。 ; 否,则进行 Checksum 计算。

;程序结束。

;清标志位 C。

JMP AAAMOV A, END ADDR2

**CMPRS** A, Y

Υ

; 是则检查 Y 的地址是否为用户程序结束地址中间地址。 **JMP** AAA ; 否,则进行 Checksum 计算。

**JMP** CHECKSUM\_END ; 是则 Checksum 计算结束。

Y\_ADD\_1:

**INCMS**

NOP

**JMP**

@B ; 跳转到 Checksum 计算。

CHECKSUM\_END:

END\_USER\_CODE:

## 2.1.2 编译选项表(CODE OPTION)

| 编译选项         | 配置项目      | 功能说明                                       |

|--------------|-----------|--------------------------------------------|

|              | RC        | 外部高速时钟振荡器采用廉价的 RC 振荡电路, XOUT 是 Fcpu 的输出引脚。 |

| High_Clk     | 12M X'tal | 外部高速时钟振荡器采用高频晶体/陶瓷振荡器(如 12MHz~16MHz)。      |

|              | 4M X'tal  | 外部高速时钟振荡器采用标准晶体/陶瓷振荡器(如 4M~10MHz)。         |

|              | Always_On | 始终开启看门狗定时器,即使在睡眠模式和绿色模式下也处于开启状态。           |

| Watch_Dog    | Enable    | 开启看门狗定时器,但在睡眠模式下关闭;                        |

| Water_bog    | Lilable   | 看门狗定时器在绿色模式下处于开启状态。                        |

|              | Disable   | 关闭看门狗定时器。                                  |

|              | Fhosc/1   | 指令周期 = 1 个时钟周期,在 Fosc/1 的选项时必须关闭杂讯滤波功能。    |

|              | Fhosc/2   | 指令周期 = 2 个时钟周期,在 Fosc/2 的选项时必须关闭杂讯滤波功能。    |

|              | Fhosc/4   | 指令周期 = 4 个时钟周期。                            |

| Fcpu         | Fhosc/8   | 指令周期 = 8 个时钟周期。                            |

| Гори         | Fhosc/16  | 指令周期 = 16 个时钟周期。                           |

|              | Fhosc/32  | 指令周期 = 32 个时钟周期。                           |

|              | Fhosc/64  | 指令周期 = 64 个时钟周期。                           |

|              | Fhosc/128 | 指令周期 = 128 个时钟周期。                          |

| Security     | Enable    | ROM 代码加密。                                  |

| Security     | Disable   | ROM 代码不加密。                                 |

| Noise Filter | Enable    | 开启杂讯滤波功能。                                  |

| Noise_Filter | Disable   | 禁止杂讯滤波功能。                                  |

- ▶ 注:

- 1、在干扰严重的情况下,建议开启杂讯滤波功能,并将 Watch\_Dog 设置为"Always\_On";

- 2、编译选项 Fcpu 仅针对高速时钟,在低速模式下 Fcpu = Flosc/4;

- 3、在外部 RC 模式下,由编译器开启杂讯滤波功能;

- 4、在设置 Watch\_Dog 的编译选项为 "Enable"时,看门狗定时器在绿色模式下继续工作。

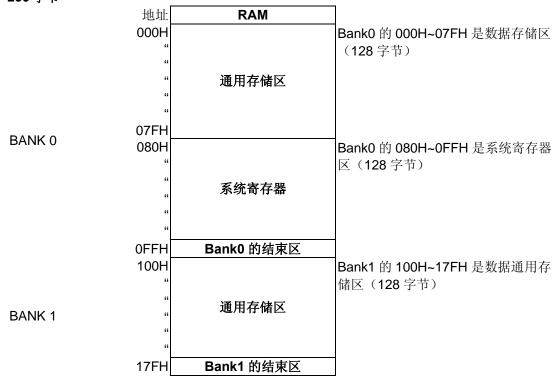

## 2.1.3 数据存储器(RAM)

SN8P2700A 单片机的片内 RAM 共有 384 个存储单元,地址范围为 000H~17FH。片内寄存器可分为通用数据存储 区和系统存储器两大部分。其中通用数据存储区共有 256 个存储单元,分为两个区域。通用数据存储区可存放用户自定义的变量,临时数据变量和中间数据变量,而系统寄存器则用来控制片内外设或表示外设的状态。

### ☞ RAM: 256 字节

#### 系统寄存器 2.1.4

## 2.1.4.1 系统寄存器列表

|   | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | Α     | В     | С     | D     | Е     | F     |

|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 8 | L     | Н     | R     | Z     | Υ     | Х     | PFLAG | RBANK | -     | -     | -     | -     | -     | -     | -     | -     |

| 9 | -     | -     | 1     | -     | -     | -     | -     | -     | -     | -     | 1     | -     | -     | 1     | -     | -     |

| Α | -     | -     | -     | -     | -     | -     | =     | -     | -     | -     | -     | -     | -     | -     | P4CON | -     |

| В | DAM   | ADM   | ADB   | ADR   | SIOM  | SIOR  | SIOB  | -     | -     | -     | -     | -     | -     | -     | -     | PEDGE |

| С | P1W   | P1M   | P2M   | P3M   | P4M   | P5M   | -     | -     | INTRQ | INTEN | OSCM  | -     | WDTR  | TC0R  | PCL   | PCH   |

| D | P0    | P1    | P2    | P3    | P4    | P5    | -     | -     | TOM   | T0C   | TC0M  | TC0C  | TC1M  | TC1C  | TC1R  | STKP  |

| Ε | P0UR  | P1UR  | P2UR  | P3UR  | P4UR  | P5UR  | @HL   | @YZ   | -     | -     | -     | -     | -     | -     | -     | -     |

| F | STK7L | STK7H | STK6L | STK6H | STK5L | STK5H | STK4L | STK4H | STK3L | STK3H | STK2L | STK2H | STK1L | STK1H | STK0L | STK0H |

## 2.1.4.2 系统寄存器说明

P4CON = P4 配置控制寄存器

= 专用寄存器,@HL间接寻址寄存器 L, H R = 工作寄存器和 ROM 查表数据缓存器

Χ = 专用寄存器, ROM 寻址寄存器 Y, Z = 专用寄存器,@YZ间接寻址寄存器,ROM 寻址寄存器

PFLAG = ROM 页及特殊标志寄存器 RBANK = RAM bank 选择寄存器 DAM = DAC 模式寄存器 ADM = ADC 模式寄存器

ADB = ADC 数据缓存器 ADR = ADC 精度选择寄存器 SIOM = SIO 模式控制寄存器 SIOR = SIO 时钟重装缓存器 SIOB P1W

= SIO 数据缓存器 = P1 口的唤醒功能寄存器 PnM = Pn 输入/输出模式控制寄存器 Pn = Pn 数据缓存器

INTRQ = 中断请求寄存器 INTEN = 中断使能寄存器 OSCM = 振荡模式控制寄存器 PCH, PCL = 程序计数器 TOM = T0 模式寄存器 TC0M = TC0 模式寄存器 = T0 计数寄存器 T0C TC0C = TC0 计数寄存器

TC1M = TC1 模式寄存器 TC0R = TC0 自动装载数据缓存器 TC1C = TC1 计数寄存器 TC1R = TC1 自动装载数据缓存器

STKP STK0~STK7 = 堆栈缓存器 = 堆栈指针缓存器 @HL = 间接寻址寄存器 @YZ = 间接寻址寄存器

## 2.1.4.3 系统寄存器的位定义

| 地址           | Bit7          | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0           | R/W        | 备注             |

|--------------|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|------------|----------------|

| 080H         | LBIT7         | LBIT6           | LBIT5           | LBIT4           | LBIT3           | LBIT2           | LBIT1           | LBIT0          | R/W        | L              |

| 081H         | HBIT7         | HBIT6           | HBIT5           | HBIT4           | HBIT3           | HBIT2           | HBIT1           | HBIT0          | R/W        | Н              |

| 082H         | RBIT7         | RBIT6           | RBIT5           | RBIT4           | RBIT3           | RBIT2           | RBIT1           | RBIT0          | R/W        | R              |

| 083H         | ZBIT7         | ZBIT6           | ZBIT5           | ZBIT4           | ZBIT3           | ZBIT2           | ZBIT1           | ZBIT0          | R/W        | Z              |

| 084H         | YBIT7         | YBIT6           | YBIT5           | YBIT4           | YBIT3           | YBIT2           | YBIT1           | YBIT0          | R/W        | Y              |

| 085H         | XBIT7<br>NT0  | XBIT6<br>NPD    | XBIT5           | XBIT4           | XBIT3           | XBIT2<br>C      | XBIT1<br>DC     | XBIT0<br>Z     | R/W<br>R/W | X<br>PFLAG     |

| 086H<br>087H | -             | - NPD           | -               | -               | -               | -               | -<br>-          | RBNKS0         | R/W        | RBANK          |

| 0AEH         | P4CON7        | P4CON6          | P4CON 5         | P4CON4          | P4CON3          | P4CON2          | P4CON1          | P4CON0         | W          | P4CON          |

| 0B0H         | DAENB         | DAB6            | DAB5            | DAB4            | DAB3            | DAB2            | DAB1            | DAB0           | R/W        | DAM 数据寄存器      |

| 0B011        | ADENB         | ADS             | EOC             | GCHS            | -               | CHS2            | CHS1            | CHS0           | R/W        | ADM 模式寄存器      |

| 0B2H         | ADB11         | ADB10           | ADB9            | ADB8            | ADB7            | ADB6            | ADB5            | ADB4           | R          | ADB 数据缓存器      |

| 0B3H         | ADCKS2        | ADCKS1          | ADLEN           | ADCKS0          | ADB3            | ADB2            | ADB1            | ADB0           | R/W        | ADR 寄存器        |

| 0B4H         | SENB          | START           | SRATE1          | SRATE0          | 0               | SCKMD           | SEDGE           | TXRX           | R/W        | SIOM 模式寄存器     |

| 0B5H         | SIOR7         | SIOR6           | SIOR5           | SIOR4           | SIOR3           | SIOR2           | SIOR1           | SIOR0          | W          | SIOR 重装缓存器     |

| 0B6H         | SIOB7         | SIOB6           | SIOB5           | SIOB4           | SIOB3           | SIOB2           | SIOB1           | SIOB0          | R/W        | SIOB 数据缓存器     |

| 0B8H         |               |                 |                 |                 |                 | P02M            | P01M            | P00M           | R/W        | P0M            |

| 0BFH         | -             | -               | -               | P00G1           | P00G0           | -               | -               | -              | R/W        | PEDGE          |

| 0C0H         | P17W          | P16W            | P15W            | P14W            | P13W            | P12W            | P11W            | P10W           | W          | P1W 唤醒功能寄存器    |

| 0C1H         | P17M          | P16M            | P15M            | P14M            | P13M            | P12M            | P11M            | P10M           | R/W        | P1M I/O 模式     |

| 0C2H         | P27M          | P26M            | P25M            | P24M            | P23M            | P22M            | P21M            | P20M           | R/W        | P2M I/O 模式     |

| 0C3H         | -             | -               | -               | -               | -               | -               | -               | P30M           | R/W        | P3M I/O 模式     |

| 0C4H         | P47M          | P46M            | P45M            | P44M            | P43M            | P42M            | P41M            | P40M           | R/W        | P4M I/O 模式     |

| 0C5H         | P57M          | P56M            | P55M            | P54M            | P53M            | P52M            | P51M            | P50M           | R/W        | P5M I/O 模式     |

| 0C8H         | ADCIRQ        | TC1IRQ          | TC0IRQ          | TOIRQ           | SIOIRQ          | P02IRQ          | P01IRQ          | P00IRQ         | R/W        | INTRQ          |

| 0C9H<br>0CAH | ADCIEN        | TC1IEN          | TC0IEN          | T0IEN<br>CPUM1  | SIOIEN<br>CPUM0 | P02IEN<br>CLKMD | P01IEN<br>STPHX | P00IEN         | R/W<br>R/W | INTEN<br>OSCM  |

| 0CCH         | WDTR7         | WDTR6           | WDTR5           | WDTR4           | WDTR3           | WDTR2           | WDTR1           | WDTR0          | W          | WDTR           |

| 0CDH         | TC0R7         | TC0R6           | TC0R5           | TC0R4           | TC0R3           | TC0R2           | TC0R1           | TC0R0          | W          | TC0R           |

| 0CEH         | PC7           | PC6             | PC5             | PC4             | PC3             | PC2             | PC1             | PC0            | R/W        | PCL            |

| 0CFH         | -             | -               | -               | -               | PC11            | PC10            | PC9             | PC8            | R/W        | PCH            |

| 0D0H         | -             | -               | -               | -               | -               | P02             | P01             | P00            | R/W        | P0 数据缓存器       |

| 0D1H         | -             | -               | P15             | P14             | P13             | P12             | P11             | P10            | R/W        | P1 数据缓存器       |

| 0D2H         | P27           | P26             | P25             | P24             | P23             | P22             | P21             | P20            | R/W        | P2 数据缓存器       |

| 0D3H         | -<br>D47      | -<br>D40        | -<br>D45        | -<br>D44        | -<br>D40        | -<br>D40        | -<br>D44        | P30            | R/W        | P3 数据缓存器       |

| 0D4H         | P47           | P46             | P45             | P44             | P43             | P42             | P41             | P40            | R/W        | P4 数据缓存器       |

| 0D5H         | P57           | P56             | P55             | P54             | P53             | P52             | P51             | P50            | R/W        | P5 数据缓存器       |

| 0D8H<br>0D9H | T0ENB<br>T0C7 | T0rate2<br>T0C6 | T0rate1<br>T0C5 | T0rate0<br>T0C4 | T0C3            | T0C2            | T0C1            | T0C0           | R/W<br>R/W | TOM<br>TOC     |

| 0DAH         | TC0ENB        | TC0rate2        | TC0rate1        | TC0rate0        | TC0CKS          | ALOAD0          | TC0OUT          |                |            | TCOM           |

| 0DBH         | TC0C7         | TC0C6           | TC0C5           | TC0C4           | TC0C3           | TC0C2           | TC0C1           | TC0C0          | R/W        | TC0C           |

| 0DCH         | TC1ENB        | TC1rate2        | TC1rate1        | TC1rate0        | TC1CKS          | ALOAD1          | TC10UT          | PWM1OUT        | R/W        | TC1M           |

| 0DDH         | TC1C7         | TC1C6           | TC1C5           | TC1C4           | TC1C3           | TC1C2           | TC1C1           | TC1C0          | R/W        | TC1C           |

| 0DEH         | TC1R7         | TC1R6           | TC1R5           | TC1R4           | TC1R3           | TC1R2           | TC1R1           | TC1R0          | W          | TC1R           |

| 0DFH         | GIE           | -               | -               | -               | STKPB3          | STKPB2          | STKPB1          | STKPB0         | R/W        | STKP 堆栈指针      |

| 0E0H<br>0E1H | -<br>P17R     | -<br>P16R       | -<br>P15R       | -<br>P14R       | -<br>P13R       | P02R<br>P12R    | P01R<br>P11R    | P00R<br>P10R   | W          | P0UR<br>P1UR   |

| 0E1H         | P27R          | P26R            | P25R            | P24R            | P23R            | P22R            | P21R            | P20R           | W          | P2UR           |

| 0E3H         | -             | -               | -               | -               | -               | -               | -               | P30R           | W          | P3UR           |

| 0E4H         | P47R          | P46R            | P45R            | P44R            | P43R            | P42R            | P41R            | P40R           | W          | P4UR           |

| 0E5H         | P57R          | P56R            | P54R            | P54R            | P53R            | P52R            | P51R            | P50R           | W          | P5UR           |

| 0E6H         | @HL7          | @HL6            | @HL5            | @HL4            | @HL3            | @HL2            | @HL1            | @HL0           | R/W        | @HL 间接寻址寄存器    |

| 0E7H         | @YZ7          | @YZ6            | @YZ5            | @YZ4            | @YZ3            | @YZ2            | @YZ1            | @YZ0           | R/W        | @YZ间接寻址寄存器     |

| 0E9H         | -             | -               | -               | -               | -               | P52OC           | P110C           | P10OC          | W          | P1OC           |

| 0F0H         | S7PC7         | S7PC6           | S7PC5           | S7PC4           | S7PC3           | S7PC2           | S7PC1           | S7PC0          | R/W<br>R/W | STK7L          |

| 0F1H<br>0F2H | S6PC7         | S6PC6           | S6PC5           | S6PC4           | S7PC11<br>S6PC3 | S7PC10<br>S6PC2 | S7PC9<br>S6PC1  | S7PC8<br>S6PC0 | R/W        | STK7H<br>STK6L |

| 0F3H         | -             | -               | -               | -               | S6PC11          | S6PC10          | S6PC9           | S6PC8          | R/W        | STK6H          |

| 0F4H         | S5PC7         | S5PC6           | S5PC5           | S5PC4           | S5PC3           | S5PC2           | S5PC1           | S5PC0          | R/W        | STK5L          |

| 0F5H         | -             | -               | -               | -               | S5PC11          | S5PC10          | S5PC9           | S5PC8          | R/W        | STK5H          |

| 0F6H         | S4PC7         | S4PC6           | S4PC5           | S4PC4           | S4PC3           | S4PC2           | S4PC1           | S4PC0          | R/W        | STK4L          |

| 0F7H         | -<br>C2DC7    | - C2DC6         | -<br>C2DCE      | -<br>C2DC4      | S4PC11          | S4PC10          | S4PC9           | S4PC8          | R/W        | STK4H          |

| 0F8H<br>0F9H | S3PC7         | S3PC6           | S3PC5           | S3PC4           | S3PC3<br>S3PC11 | S3PC2<br>S3PC10 | S3PC1<br>S3PC9  | S3PC0<br>S3PC8 | R/W<br>R/W | STK3L<br>STK3H |

| 0FAH         | S2PC7         | S2PC6           | S2PC5           | S2PC4           | S2PC3           | S2PC2           | S2PC1           | S2PC0          | R/W        | STK2L          |

| 0FBH         | -             |                 |                 |                 | S2PC11          | S2PC10          | S2PC9           | S2PC8          | R/W        | STK2H          |

|              |               |                 |                 |                 |                 |                 |                 |                |            |                |

| 地址   | Bit7  | Bit6  | Bit5  | Bit4  | Bit3   | Bit2   | Bit1  | Bit0  | R/W | 备注    |

|------|-------|-------|-------|-------|--------|--------|-------|-------|-----|-------|

| 0FCH | S1PC7 | S1PC6 | S1PC5 | S1PC4 | S1PC3  | S1PC2  | S1PC1 | S1PC0 | R/W | STK1L |

| 0FDH | -     | -     | -     | -     | S1PC11 | S1PC10 | S1PC9 | S1PC8 | R/W | STK1H |

| 0FEH | S0PC7 | S0PC6 | S0PC5 | S0PC4 | S0PC3  | S0PC2  | S0PC1 | S0PC0 | R/W | STK0L |

| 0FFH | -     | -     | -     | -     | S0PC11 | S0PC10 | S0PC9 | S0PC8 | R/W | STK0H |

- \* 注:

- 1、为了避免系统错误,在初始化时,请将上表所有寄存器的位都按照设计要求设置为确定的"1"或者"0";

- 2、所有寄存器名都已在 SN8ASM 编译器中做了宣告:

- 3、用户使用 SN8ASM 编译器对寄存器的位进行操作时,须在该寄存器的位前加 "F";

- 4、指令"b0bset","b0bclr","bset","bclr"只能用于可读写的寄存器("R/W")。

### 2.1.4.4 累加器

8 位数据寄存器 ACC 用来执行 ALU 与数据存储器之间数据的传送操作。如果操作结果为零(Z)或有进位产生(C 或 DC),程序状态寄存器 PFLAG 中相应位会发生变化。

ACC 并不在 RAM 中,因此在立即寻址模式中不能用"BOMOV"指令对其进行读写。

#### ▶ 例:读/写 ACC。

:将立即数写入ACC。

MOV A, #0FH

;把 ACC 中的数据存入 BUF 中。

MOV BUF, A BOMOV BUF, A

;把 BUF 中的数据送到 ACC 中。

MOV A, BUF BOMOV A, BUF

系统执行中断操作时, ACC 的数据不会自动存储, 用户需通过程序将中断入口处的 ACC 的数据送入存储器进行保存。可通过"PUSH"和"POP"指令对系统寄存器 80H~87H 的状态进行存储及恢复。

#### ▶ 例: ACC 和工作寄存器中断保护操作。

.DATA ACCBUF DS 1 ; 定义 ACCBUF 为 ACC 数据存储单元。

.CODE

INT\_SERVICE:

B0XCH A, ACCBUF ; ACC 数据送入缓存器。

PUSH ; PFLAG 等数据送入缓存器。

•••

POP

;恢复 PFLAG。

B0XCH A, ACCBUF ; 恢复 ACC。

RETI ; 退出中断。

\* 注:必须使用"B0XCH"指令进行 ACC 数据的中断恢复,否则 PFLAG 会被更改而导致出错。

## 2.1.4.5 程序状态寄存器PFLAG

寄存器PFLAG中包含ALU运算状态信息、系统复位状态信息和LVD低电压检测状态信息。其中,位NTO和NPD显示系统复位状态信息,包括上电复位、LVD复位、外部复位和看门狗复位;位C、DC和Z显示ALU的运算信息。

| 086H  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG | NT0   | NPD   | -     | -     | -     | С     | DC    | Z     |

| 读/写   | R/W   | R/W   | -     | -     | 1     | R/W   | R/W   | R/W   |

| 复位后   | Х     | X     | -     | -     | -     | 0     | 0     | 0     |

Bit [7:6] NTO, NPD: 复位状态标志。

| NT0 | NPD | 复位状态   |

|-----|-----|--------|

| 0   | 0   | 看门狗复位  |

| 0   | 1   | 保留     |

| 1   | 0   | LVD 复位 |

| 1   | 1   | 外部复位   |

- Bit 2 **C:** 进位标志。

- 1 =加法运算后有进位、减法运算没有借位发生或移位后移出逻辑"1"或比较运算的结果≥0;

- 0=加法运算后没有进位、减法运算有借位发生或移位后移出逻辑"0"或比较运算的结果<0。

- **DC:** 辅助进位标志。

- 1=加法运算时低四位有进位,或减法运算后没有向高四位借位;

- 0=加法运算时低四位没有进位,或减法运算后有向高四位借位。

- Bit 0 **Z**: 零标志。

- 1=算术/逻辑/分支转移运算的结果为零;

- 0=算术/逻辑/分支转移运算的结果非零。

- \* 注:关于标志位 C、DC 和 Z 的更多信息请参阅指令集相关内容。

## 2.1.4.6 程序计数器

程序计数器 PC 是一个 12 位二进制程序地址寄存器,分高 4 位和低 8 位。专门用来存放下一条需要执行指令的内存地址。通常,程序计数器会随程序中指令的执行自动增加。

若程序执行 CALL 和 JMP 指令时, PC 指向特定的地址。

|     | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| PC  | -      | -      | -      | -      | PC11   | PC10   | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| 复位后 | -      | -      | -      | -      | 0      | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|     |        | PCH    |        |        |        |        |       |       |       |       |       | P(    | CL    |       |       |       |

#### ☞ 单地址跳转

在 SONiX 单片机里面,有 9 条指令(CMPRS、INCS、INCMS、DECS、DECMS、BTS0、BTS1、B0BTS0 和 B0BTS1)可完成单地址跳转功能。如果这些指令执行结果为真,那么 PC 值加 2 以跳过下一条指令。

; 否则执行 COSTEP。

如果位测试为真, PC 加 2。

B0BTS1 FC

; 若 Carry\_flag = 1 则跳过下一条指令。

JMP C0STEP

COSTEP: NOP

B0MOV A, BUF0 ; BUF0 送入 ACC。

BOBTSO FZ ; Zero flag = 0 则跳过下一条指令。

JMP C1STEP ; 否则执行 C1STEP。

C1STEP: NOP

如果 ACC 等于指定的立即数则 PC 值加 2, 跳过下一条指令。

CMPRS A, #12H

JMP COSTEP

COSTEP: NOP

执行加 1 指令后,结果为零时,PC 的值加 2,跳过下一条指令。

INCS:

INCS BUF0

JMP COSTEP ;如果 ACC 不为 "0" ,则跳至 COSTEP。

COSTEP: NOP

INCMS:

INCMS BUF0

JMP COSTEP ;如果 BUF0 不为"0",则跳至 COSTEP。

COSTEP: NOP

执行减1指令后,结果为零时,PC的值加2,跳过下一条指令。

DECS:

DECS BUF0

JMP COSTEP ;如果 ACC 不为"0",则跳至 COSTEP。

COSTEP: NOP

DECMS:

DECMS BUF0

JMP COSTEP ;如果 BUF0 不为"0",则跳至 COSTEP。

COSTEP: NOP

#### ☞ 多地址跳转

执行 JMP 或 ADD M,A(M=PCL)指令可实现多地址跳转。执行 ADD M, A、ADC M, A 或 B0ADD M, A 后,若 PCL 溢出,PCH 会自动进位。对于跳转表及其它应用,用户可以通过上述 3 条指令计算 PC 的值而不需要担心 PCL 溢出的问题。

\* 注:PCH 仅支持 PC 的递增运算而不支持递减运算。当 PCL+ACC 执行完 PCL 有进位时,PCH 会自动加 1,但执行 PCL-ACC 有借位发生,PCH 的值会保持不变。

▶ 例: PC = 0323H (PCH = 03H, PCL = 23H)。

; PC = 0323H

MOV A, #28H B0MOV PCL, A

PCL, A ; 跳到地址 0328H。

• • •

; PC = 0328H

MOV A, #00H

BOMOV PCL, A ; 跳到地址 0300H。

...

➢ 例: PC = 0323H (PCH = 03H, PCL = 23H)。

PC = 0323H

B0ADD

PCL, A

; PCL = PCL + ACC, PCH 的值不变。

JMP

A0POINT

; ACC = 0, 跳到 A0POINT。

JMP

A1POINT

; ACC = 1, 跳到 A1POINT。

JMP

A3POINT

; ACC = 3, 跳到 A3POINT。

..

...

## 2.1.4.7 H, L寄存器

寄存器 H 和 L 都是 8 位缓存器, 主要有以下两个功能:

- 通用工作寄存器;

- RAM 数据寻址指针@HL。

| 081H | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Н    | HBIT7 | HBIT6 | HBIT5 | HBIT4 | HBIT3 | HBIT2 | HBIT1 | HBIT0 |

| 读/写  | R/W   |

| 复位后  | X     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |

| H080 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| L    | LBIT7 | LBIT6 | LBIT5 | LBIT4 | LBIT3 | LBIT2 | LBIT1 | LBIT0 |

| 读/写  | R/W   |

| 复位后  | Х     | X     | X     | Х     | X     | Х     | Х     | X     |

例:用 H、L 作为数据指针,访问 bank0 中 020H 处的内容。

**B0MOV** H, #00H **B0MOV** L, #20H **B0MOV** A, @HL

例:对 bank 0 中的数据进行清零处理。

CLR

; H = 0, 指向 bank 0。

**B0MOV** L, #7FH ; L = 7FH.

CLR\_HL\_BUF:

CLR @HL ;@HL 清零。

**DECMS** ; L-1, 如果 L=0, 程序结束。

JMP CLR\_HL\_BUF

@HL CLR

END\_CLR:

## 2.1.4.8 Y, Z寄存器

寄存器 Y 和 Z 都是 8 位缓存器, 主要用途如下:

- 普通工作寄存器;

- RAM 数据寻址指针@YZ;

- 配合指令 MOVC 对 ROM 数据进行查表。

| 084H | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Υ    | YBIT7 | YBIT6 | YBIT5 | YBIT4 | YBIT3 | YBIT2 | YBIT1 | YBIT0 |

| 读/写  | R/W   |

| 复位后  | X     | Х     | Х     | Х     | Х     | Х     | X     | Х     |

| 083H | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Z    | ZBIT7 | ZBIT6 | ZBIT5 | ZBIT4 | ZBIT3 | ZBIT2 | ZBIT1 | ZBIT0 |

| 读/写  | R/W   |

| 复位后  | X     | Х     | Х     | X     | Х     | Х     | X     | Х     |

例:用Y、Z作为数据指针,访问 bank0 中 025H 处的内容。

B0MOV Y, #00H ; Y 指向 RAM bank 0。 B0MOV Z, #25H ; Z 指向 25H。 B0MOV A, @YZ ; 数据送入 ACC。

▶ 例:利用数据指针@YZ 对 RAM 数据清零。

B0MOV Y, #0 ; Y = 0, 指向 bank 0。

BOMOV Z, #7FH ; Z = 7FH, RAM 区的最后单元。

CLR\_YZ\_BUF:

CLR @YZ ; @YZ清零。

DECMS Z ;

JMP CLR\_YZ\_BUF ; 不为零。

CLR @YZ

END\_CLR: ;

. . .

### 2.1.4.9 X寄存器

8 位缓存器 X 寄存器主要有以下两个功能:

- 通用工作寄存器;

- 查表时为 ROM 的数据指针。

| 085H | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| X    | XBIT7 | XBIT6 | XBIT5 | XBIT4 | XBIT3 | XBIT2 | XBIT1 | XBIT0 |

| 读/写  | R/W   |

| 复位后  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

注:关于 X 寄存器的查表应用请参阅"查表"章节。

## 2.1.4.10 R寄存器

8 位缓存器 R 主要有以下两个功能:

- 作为工作寄存器使用;

- **存储执行查表指令后的高字节数据。**(执行 MOVC 指令,指定 ROM 单元的高字节数据会被存入 R 寄存器而低字节数据则存入 ACC。)

| 082H | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| R    | RBIT7 | RBIT6 | RBIT5 | RBIT4 | RBIT3 | RBIT2 | RBIT1 | RBIT0 |

| 读/写  | R/W   |

| 复位后  | Х     | X     | Х     | Χ     | Х     | Х     | Χ     | X     |

# 2.2 寻址模式

## 2.2.1 立即寻址

将立即数直接送入 ACC 或指定的 RAM 单元。

▶ 例:立即数 12H 送入 ACC。

MOV A, #12H

▶ 例:立即数 12H 送入寄存器 R。

B0MOV R, #12H

注: 立即寻址模式中,指定的 RAM 单元必须是 80H~87H 的工作寄存器。

## 2.2.2 直接寻址

通过 ACC 对 RAM 单元数据进行操作。

▶ 例:地址 12H 处的内容送入 ACC。

B0MOV A, 12H

➢ 例: ACC 中数据写入 RAM 中 12H 单元。

B0MOV 12H, A

## 2.2.3 间接寻址

通过数据指针(H/L、Y/Z)对数据存储单元进行读写。

例:通过指针@HL间接寻址。

B0MOV H, #0 ; 清 "H" 以寻址 RAM bank 0。

BOMOV L, #12H ; 设定寄存器地址。

B0MOV A, @HL

》 例: 通过指针@YZ 间接寻址。

B0MOV Y, #0 ; 清 "Y" 以寻址 RAM bank 0。

BOMOV Z, #12H ; 设定寄存器地址。

BOMOV A, @YZ

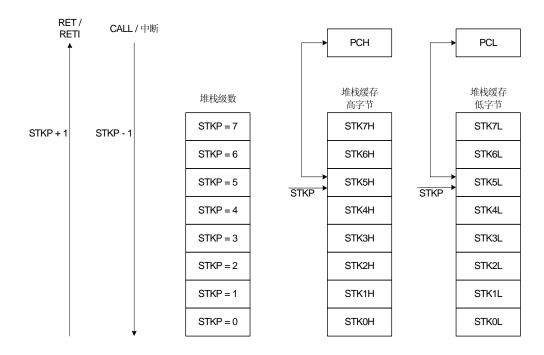

# 2.3 堆栈

## 2.3.1 概述

SN8P2700A 的堆栈缓存器共有 8 层 程序进入中断或执行 CALL 指令时, 用来存储程序计数器 PC 的值。寄存器 STKP 为堆栈指针, 指向堆栈缓存器顶层, STKnH 和 STKnL 分别是各堆栈缓存器高、低字节。

## 2.3.2 堆栈寄存器

堆栈指针 STKP 是一个 3 位寄存器,存放被访问的堆栈单元地址,12 位数据存储器 STKnH 和 STKnL 用于暂存堆栈数据。以上寄存器都位于 bank 0。

堆栈操作遵循后进先出(LIFO)的原则,入栈时堆栈指针 STKP 的值减 1,出栈时 STKP 的值加 1,这样,STKP 总是指向堆栈缓存器项层单元。

系统进入中断或执行 CALL 指令之前,程序计数器 PC 的值被存入堆栈缓存器中进行入栈保护。

| 0DFH | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|------|-------|-------|-------|-------|-------|--------|--------|--------|

| STKP | GIE   |       |       | -     | -     | STKPB2 | STKPB1 | STKPB0 |

| 读/写  | R/W   | -     | -     | -     | -     | R/W    | R/W    | R/W    |

| 复位后  | 0     | 1     | 1     | -     | -     | 1      | 1      | 1      |

Bit[2:0] **STKPBn**: 堆栈指针(n=0~2)。

Bit 7 GIE: 全局中断控制位。

0 = 禁止; 1 = 允许。

▶ 例:系统复位时,堆栈指针寄存器内容为默认值,但强烈建议在程序初始部分重新设定,如下面所示:

MOV A, #00000111B B0MOV STKP, A

| 0F0H~0FFH | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|-------|--------|--------|-------|-------|

| STKnH     | •     | -     | -     | -     | SnPC11 | SnPC10 | SnPC9 | SnPC8 |

| 读/写       | -     | -     | -     | -     | R/W    | R/W    | R/W   | R/W   |

| 复位后       | -     | -     | -     | -     | 0      | 0      | 0     | 0     |

| 0F0H~0FFH | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| STKnL     | SnPC7 | SnPC6 | SnPC5 | SnPC4 | SnPC3 | SnPC2 | SnPC1 | SnPC0 |

| 读/写       | R/W   |

| 复位后       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

STKn = STKnH, STKnL  $(n = 7 \sim 0)$  .

## 2.3.3 堆栈操作举例

执行程序调用指令 CALL 和响应中断服务时,堆栈指针 STKP 的值减 1,指针指向下一个堆栈缓存器。同时,对程序计数器 PC 的内容进行入栈保护。入栈操作如下表所示:

| 堆栈层数        |        | STKP   |        | 堆栈组   | 爰存器   | 注释        |

|-------------|--------|--------|--------|-------|-------|-----------|

| <b>堆似层数</b> | STKPB2 | STKPB1 | STKPB0 | 高字节   | 低字节   | <b>江仲</b> |

| 0           | 1      | 1      | 1      | Free  | Free  | =         |

| 1           | 1      | 1      | 0      | STK0H | STK0L | •         |

| 2           | 1      | 0      | 1      | STK1H | STK1L | =         |

| 3           | 1      | 0      | 0      | STK2H | STK2L | •         |

| 4           | 0      | 1      | 1      | STK3H | STK3L | -         |

| 5           | 0      | 1      | 0      | STK4H | STK4L | •         |

| 6           | 0      | 0      | 1      | STK5H | STK5L | •         |

| 7           | 0      | 0      | 0      | STK6H | STK6L | -         |

| 8           | 1      | 1      | 1      | STK7H | STK7L | =         |

| > 8         | 1      | 1      | 0      | -     | -     | 堆栈溢出      |

对应每个入栈操作,都有一个出栈操作来恢复程序计数器 PC 的值。RETI 指令用于中断服务程序中,RET 用于子程序调用。出栈时,STKP 加 1 并指向下一个空闲堆栈缓存器。堆栈恢复操作如下表所示:

|      | 7 7.147. | STKP   |        |       | 爰存器   |    |

|------|----------|--------|--------|-------|-------|----|

| 堆栈层数 | STKPB2   | STKPB1 | STKPB0 | 高字节   | 低字节   | 注释 |

| 8    | 1        | 1      | 1      | STK7H | STK7L | -  |

| 7    | 0        | 0      | 0      | STK6H | STK6L | -  |

| 6    | 0        | 0      | 1      | STK5H | STK5L | -  |

| 5    | 0        | 1      | 0      | STK4H | STK4L | -  |

| 4    | 0        | 1      | 1      | STK3H | STK3L | -  |

| 3    | 1        | 0      | 0      | STK2H | STK2L | -  |

| 2    | 1        | 0      | 1      | STK1H | STK1L | -  |

| 1    | 1        | 1      | 0      | STK0H | STK0L | -  |

| 0    | 1        | 1      | 1      | Free  | Free  | -  |

# 3 复位

## 3.1 概述

SN8P2700A 系列的单片机有以下几种复位方式:

- 上电复位;

- 看门狗复位;

- LVD 检测复位;

- 外部复位。

上述任一种复位发生时,所有的系统寄存器恢复默认状态,程序停止运行,同时程序计数器 PC 清零。复位结束后,系统从向量 0000H 处重新开始运行。PFLAG 寄存器的 NTO 和 NPD 两个标志位能够给出系统复位状态的信息。用户可以编程控制 NTO 和 NPD,从而控制系统的运行路径。

| 086H  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG | NT0   | NPD   | -     | -     | -     | С     | DC    | Z     |

| 读/写   | R/W   | R/W   | -     | -     | -     | R/W   | R/W   | R/W   |

| 复位后   | Х     | Х     | -     | -     | -     | 0     | 0     | 0     |

Bit [7:6] NTO, NPD: 复位状态标志位

| NT0 | NPD | 复位情况       | 说明              |

|-----|-----|------------|-----------------|

| 0   | 0   | 看门狗复位      | 看门狗定时器溢出        |

| 0   | 1   | 系统保留       | -               |

| 1   | 0   | 上电及 LVD 复位 | 电源电压低于 LVD 检测电压 |

| 1   | 1   | 外部复位       | 外部复位引脚检测到低电平    |

任何一种复位方式都需要一定的响应时间,系统提供完善的复位流程以保证复位动作的顺利进行。对于不同类型的振荡器,完成复位所需要的时间也不同。因此,VDD的上升速度和不同晶振的起振时间都不固定。RC振荡器的起振时间最短,晶体振荡器的起振时间则较长。在用户使用的过程中,应考虑系统对上电复位时间的要求。

# 3.2 上电复位

上电复位与 LVD 操作密切相关。系统上电过程呈逐渐上升的曲线形式,需要一定时间才能达到正常电平值。下面给出上电复位的正常时序:

- 上电:系统检测到电源电压上升并等待其稳定;

- **外部复位:** 系统检测外部复位引脚状态。如果不为高电平,系统保持复位状态直到外部复位引脚的复位结束。

- 系统初始化: 所有的系统寄存器被置为默认状态;

- 振荡器开始工作:振荡器开始提供系统时钟;

- **执行程序:** 上电结束,程序开始运行。

## 3.3 看门狗复位

看门狗复位是系统的一种保护设置。在正常状态下,由程序将看门狗定时器清零。若出错,系统处于未知状态,看门 狗定时器溢出,此时系统复位。看门狗复位后,系统重启进入正常状态。看门狗复位的时序如下:

- **看门狗定时器状态:** 系统检测看门狗定时器是否溢出, 若溢出, 则系统复位;

- 系统初始化: 所有的系统寄存器被置为默认状态;

- **振荡器开始工作:** 振荡器开始提供系统时钟;

- **执行程序:** 上电结束,程序开始运行。

看门狗定时器应用注意事项如下:

- 对看门狗清零之前,检查 I/O 口的状态和 RAM 的内容可增强程序的可靠性;

- 不能在中断中对看门狗清零,否则无法侦测到主程序跑飞的状况;

- 程序中应该只在主程序中有一次清看门狗的动作,这种架构能够最大限度的发挥看门狗的保护功能。

- \* 注:关于看门狗定时器的详细内容,请参阅"看门狗定时器"有关章节。

# 3.4 掉电复位

#### 3.4.1 概述

掉电复位针对外部因素引起的系统电压跌落情形(例如:干扰或外部负载的变化),掉电复位可能会引起系统工作状态不正常或程序执行错误。

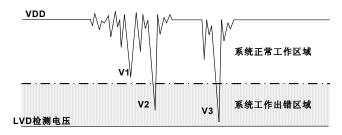

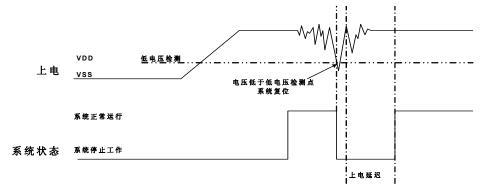

#### 掉电复位示意图

电压跌落可能会进入系统死区。系统死区意味着电源不能满足系统的最小工作电压要求。上图是一个典型的掉电复位示意图。图中,VDD 受到严重的干扰,电压值降的非常低。虚线以上区域系统正常工作,在虚线以下的区域内,系统进入未知的工作状态,这个区域称作死区。当 VDD 跌至 V1 时,系统仍处于正常状态;当 VDD 跌至 V2 和 V3 时,系统进入死区,则容易导致出错。以下情况系统可能进入死区:

#### DC 运用中:

DC 运用中一般都采用电池供电,当电池电压过低或单片机驱动负载时,系统电压可能跌落并进入死区。这时,电源不会进一步下降到 LVD 检测电压,因此系统维持在死区。

#### AC 运用中:

系统采用 AC 供电时,DC 电压值受 AC 电源中的噪声影响。当外部负载过高,如驱动马达时,负载动作产生的干扰也影响到 DC 电源。VDD 若由于受到干扰而跌落至最低工作电压以下时,则系统将有可能进入不稳定工作状态。

在 AC 运用中,系统上、下电时间都较长。其中,上电时序保护使得系统正常上电,但下电过程却和 DC 运用中情形类似,AC 电源关断后,VDD 电压在缓慢下降的过程中易进入死区。

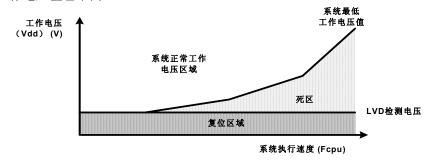

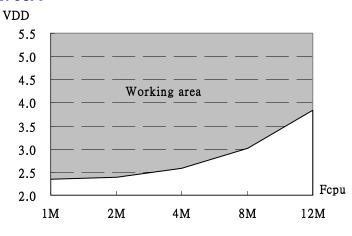

## 3.4.2 系统工作电压

为了改善系统掉电复位的性能,首先必须明确系统具有的最低工作电压值。系统最低工作电压与系统执行速度有关,不同的执行速度下最低工作电压值也不同。

#### 系统工作电压与执行速度关系图

如上图所示,系统正常工作电压区域一般高于系统复位电压,同时复位电压由低电压检测(LVD)电平决定。当系统执行速度提高时,系统最低工作电压也相应提高,但由于系统复位电压是固定的,因此在系统最低工作电压与系统复位电压之间就会出现一个电压区域,系统不能正常工作,也不会复位,这个区域即为死区。

#### 掉电复位性能改进 3.4.3

如何改善系统掉电复位性能,有以下几点建议:

- LVD 复位:

- 看门狗复位:

- 降低系统工作速度;

- 采用外部复位电路(稳压二极管复位电路,电压偏移复位电路,外部 IC 复位)。

- 注: "稳压二极管复位电路"、"电压偏移复位电路"和"外部 IC 复位"能够完全避免掉电复位出错。

#### LVD 复位:

低电压检测(LVD)是 SONiX 8 位单片机内置的掉电复位保护装置,当 VDD 跌落并低于 LVD 检测电压值时,LVD 被触发,系统复位。不同的单片机有不同的 LVD 检测电平, LVD 检测电平值仅为一个电压点,并不能覆盖所有死区范围。 因此采用 LVD 依赖于系统要求和环境状况。电源变化较大时,LVD 能够起到保护作用,如果电源变化触发 LVD,系统工 作仍出错,那么 LVD 就不能起到保护作用,就需要采用其它复位方法。

#### 看门狗复位:

看门狗定时器用于保证系统正常工作。通常,会在主程序中将看门狗定时器清零,但不要在多个分支程序中清看门狗。 若程序正常运行,看门狗不会复位。当系统进入死区或程序运行出错的时候,看门狗定时器继续计数直至溢出,系统复位。 如果看门狗复位后电源仍处于死区,则系统复位失败,保持复位状态,直到系统工作状态恢复到正常值。

#### 降低系统工作速度:

系统工作速度越快最低工作电压值越高,从而加大工作死区的范围,因此降低系统工作速度不失为降低系统进入死区 几率的有效措施。所以,可选择合适的工作速度以避免系统进入死区,这个方法需要调整整个程序使其满足系统要求。

#### 附加外部复位电路:

外部复位也能够完全改善掉电复位性能。有三种外部复位方式可改善掉电复位性能: 稳压二极管复位电路, 电压偏移 复位电路和外部 IC 复位。它们都采用外部复位信号控制单片机可靠复位。

# 3.5 外部复位

外部复位功能由编译选项 "Reset\_Pin" 控制。将该编译选项置为 "Reset",可使能外部复位功能。外部复位引脚为施密特触发结构,低电平有效。复位引脚处于高电平时,系统正常运行。当复位引脚输入低电平信号时,系统复位。外部复位操作在上电和正常工作模式时有效。需要注意的是,在系统上电完成后,外部复位引脚必须输入高电平,否则系统将一直保持在复位状态。外部复位的时序如下:

- **外部复位(当且仅当外部复位引脚为使能状态)**:系统检测复位引脚的状态,如果复位引脚不为高电平,则系统会一直保持在复位状态,直到外部复位结束;

- **系统初始化:** 所有的系统寄存器被置为初始状态;

- **振荡器开始工作:** 振荡器开始提供系统时钟;

- **执行程序:** 上电结束,程序开始运行。

外部复位可以在上电过程中使系统复位。良好的外部复位电路可以保护系统以免进入未知的工作状态,如 AC 应用中的掉电复位等。

# 3.6 外部复位电路

## 3.6.1 基本RC复位电路

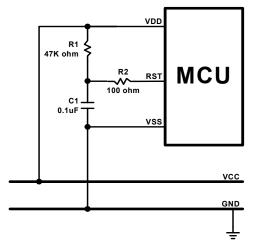

上图为一个由电阻 R1 和电容 C1 组成的基本 RC 复位电路,它在系统上电的过程中能够为复位引脚提供一个缓慢上升的复位信号。这个复位信号的上升速度低于 VDD 的上电速度,为系统提供合理的复位时序,当复位引脚检测到高电平时,系统复位结束,进入正常工作状态。

· 注:此 RC 复位电路不能解决非正常上电和掉电复位问题。

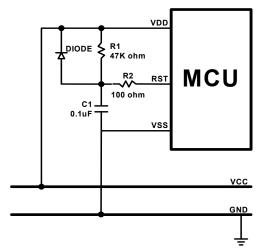

## 3.6.2 二极管及RC复位电路

上图中,R1 和C1 同样是为复位引脚提供输入信号。对于电源异常情况,二极管正向导通使C1 快速放电并与VDD保持一致,避免复位引脚持续高电平、系统无法正常复位。

☀ 注:"基本 RC 复位电路"和"二极管及 RC 复位电路"中的电阻 R2 都是必不可少的限流电阻,以避免复位引脚 ESD (Electrostatic Discharge)或 EOS(Electrical Over-stress)击穿。

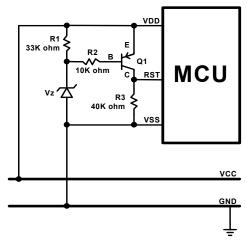

## 3.6.3 稳压二极管复位电路

稳压二极管复位电路是一种简单的 LVD 电路,基本上可以完全解决掉电复位问题。如上图电路中,利用稳压管的击穿电压作为电路复位检测值,当 VDD 高于 "Vz + 0.7V"时,三极管集电极输出高电平,单片机正常工作;当 VDD 低于 "Vz + 0.7V"时,三极管集电极输出低电平,单片机复位。稳压管规格不同则电路复位检测值不同,根据电路的要求选择合适的二极管。

## 3.6.4 电压偏移复位电路

电压偏置复位电路是一种简单的 LVD 电路,基本上可以完全解决掉电复位问题。与稳压二极管复位电路相比,这种复位电路的检测电压值的精确度有所降低。电路中,R1 和 R2 构成分压电路,当 VDD 高于和等于分压值 "0.7V x (R1 + R2) / R1"时,三极管集电极 C 输出高电平,单片机正常工作; VDD 低于 "0.7V x (R1 + R2) / R1"时,集电极 C 输出低电平,单片机复位。

对于不同应用需求,选择适当的分压电阻。单片机复位引脚上电压的变化与 VDD 电压变化之间的差值为 0.7V。如果 VDD 跌落并低于复位引脚复位检测值,那么系统将被复位。如果希望提升电路复位电平,可将分压电阻设置为 R2>R1, 并选择 VDD 与集电极之间的结电压高于 0.7V。分压电阻 R1 和 R2 在电路中要耗电,此处的功耗必须计入整个系统的功耗中。

\* 注: 在电源不稳定或掉电复位的情况下。"稳压二极管复位电路"和"偏压复位电路"能够保护电路在电压跌落时避免系统出错。 当电压跌落至低于复位检测值时,系统将被复位。从而保证系统正常工作。

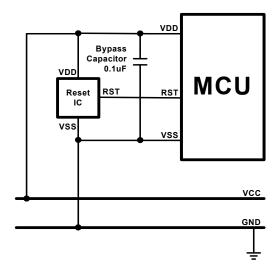

# 3.6.5 外部IC复位

# 4 系统时钟

## 4.1 概述

SN8P2700A 系列的单片机内带双时钟系统:高速时钟和低速时钟。高速时钟由外部振荡电路提供,低速时钟由内置的低速 RC 振荡电路(ILRC 16KHZ@3V、32KHz @5V)提供。两种时钟都可作为系统时钟源 Fosc,系统工作在低速模式时,Fosc 4 分频后作为一个指令周期(Fcpu)。

- 普通模式(高速时钟): Fcpu = Fhosc / N, N = 1~128, 由 Fcpu 编译选项控制;

- 低速模式(低速时钟): Fcpu = Flosc/4。

在干扰较严重的运行条件下,SONiX 提供的杂讯滤波器能够对外部干扰进行隔离以保护系统的正常工作。但在杂讯滤波器有效时,高速时钟的 Fcpu 被限制为 Fcpu=Fhosc/N, N=4~128。

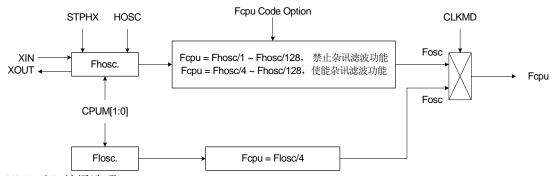

## 4.2 系统时钟框图

- HOSC: High\_Clk 编译选项。

- Fhosc: 外部高速时钟频率。

- Flosc: 内部低速 RC 时钟频率(16KHz@3V,32KHz@5V)。

- Fosc: 系统时钟频率。Fcpu: 指令执行频率。

# 4.3 OSCM寄存器

寄存器 OSCM 控制振荡器的状态和系统的工作模式。

| 0CAH | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

| OSCM | 0     | 0     | 0     | CPUM1 | CPUM0 | CLKMD | STPHX | 0     |

| 读/写  | -     | -     | -     | R/W   | R/W   | R/W   | R/W   | -     |

| 复位后  | X     | X     | X     | 0     | 0     | 0     | 0     | Х     |

Bit 1 STPHX: 高速振荡器控制位。

0 = 高速时钟正常运行;

1 = 高速振荡器停止,内部低速 RC 振荡器运行。

Bit 2 CLKMD: 系统高/低速时钟模式控制位。

0 = 普通模式,系统采用高速时钟;

1 = 低速模式,系统采用内部低速时钟。

Bit[4:3] **CPUM[1:0]**: 单片机工作模式控制位。

00 = 普通模式;

01 = 睡眠模式;

10 = 绿色模式;

11 = 系统保留。

▶ 例:停止高速振荡器。

BOBSET FSTPHX

》 例:进入睡眠模式时,停止高速及低速振荡器。

B0BSET FCPUM0

# 4.4 系统高速时钟

系统高速时钟源来自外部高速振荡器,由编译选项"High\_Clk"控制。

| High_Clk | 功能说明                              |

|----------|-----------------------------------|

| RC       | 高速时钟为外部 RC 振荡器,Xout 是 Fcpu 的输出引脚。 |

| 12M      | 高速时钟为外部高速振荡器,频率范围为 10MHz ~ 16MHz。 |

| 4M       | 高速时钟为外部振荡器,频率范围为 2MHz ~ 10MHz。    |

## 4.4.1 外部高速时钟

外部高速时钟共三种模式:石英/陶瓷振荡器,RC及外部时钟源,由编译选项 High\_Clk 控制具体模式的选择。石英/陶瓷振荡器和 RC 振荡器的起振时间各不相同。RC 振荡器的起振时间相对较短。振荡器的起振时间决定了复位时间的长短。

## 4.4.1.1 石英/陶瓷振荡器

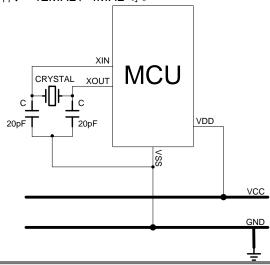

石英/陶瓷振荡器由 XIN、XOUT 口驱动,对于高速、普通和低速三种不同工作模式,振荡器的驱动电流也不同。编译选项"High\_Clk"支持不同的频率条件: 12MHz、4MHz等。

☀ 注: 上图中,XIN/XOUT/VSS 引脚与石英/陶瓷振荡器以及电容 C 之间的线路越短越好。

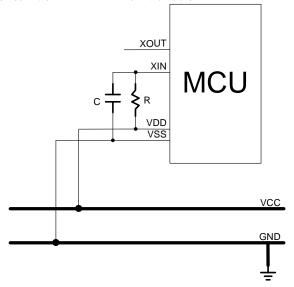

### 4.4.1.2 RC振荡器

通过编译选项"High\_Clk"的设置可控制 RC 振荡器的选择,RC 振荡器输出频率最高可达 10MHZ。改变电阻 R 可改变输出频率的大小,电容 C 的最佳容量为 50P~100P,如下图所示:

注: 电容 C 和电阻 R 应尽可能的接近单片机的 VDD。

### 4.4.1.3 外部时钟源

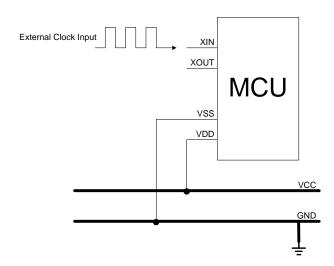

单片机可选择片外时钟信号作为系统时钟,从 XIN 脚送入。

注:外部振荡电路中的 GND 必须尽可能的接近单片机的 VSS 端口。

# 4.5 系统低速时钟

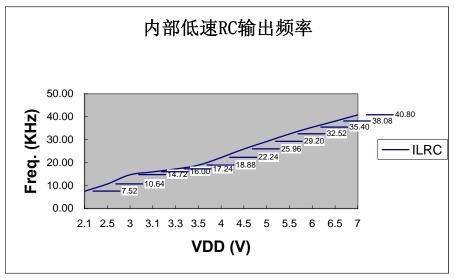

系统低速时钟源即内置的低速振荡器,采用 RC 振荡电路。低速时钟的输出频率受系统电压和环境温度的影响,通常为 5V 时输出 32KHZ, 3V 时输出 16KHZ。输出频率与工作电压之间的关系如下图所示。

低速时钟可作为看门狗定时器的时钟源。由 CLKMD 控制系统低速工作模式。

- Flosc = 内部低速 RC 振荡器(16KHz @3V, 32KHz @5V)。

- 低速模式 Fcpu = Flosc / 4。

在睡眠模式下可以停掉内部低速 RC。

例:在睡眠模式下,停止内部低速振荡器。 BOBSET FCPUMO

注:不可以单独停止内部低速时钟,由寄存器 OSCM 的位 CPUM0 和 CPUM1 的设置决定内部低速时钟的状态。

## 4.5.1 系统时钟测试

在设计过程中, 用户可通过软件指令周期对系统时钟速度进行测试。

▶ 例:外部振荡器的 Fcpu 指令周期测试。

BOBSET POM.0 ; PO.0 置为输出模式以输出 Fcpu 的触发信号。

@@:

B0BSET P0.0 B0BCLR P0.0 JMP @B

\* 注:不能直接从 XIN 引脚测试 RC 振荡频率,因为探针的连接会影响测试的准确性。

# 5 系统工作模式

# 5.1 概述

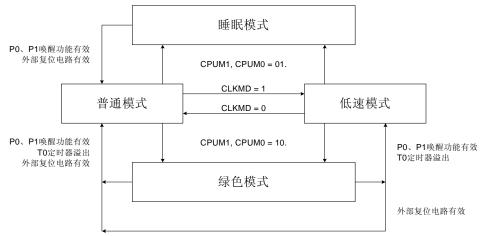

SN8P2700A 可在如下四种工作模式之间进行切换:

- 普通模式(高速模式);

- 低速模式;

- 省电模式(睡眠模式);

- 绿色模式。

系统模式切换示意图

#### 工作模式说明

| 工作模式           | 普通模式                  | 低速模式       | 绿色模式        | 睡眠模式     | 注释              |

|----------------|-----------------------|------------|-------------|----------|-----------------|

| EHOSC          | 运行                    | 由 STPHX 控制 | 由 STPHX 控制  | 停止       |                 |

| ILRC           | 运行    运行              |            | 运行          | 停止       |                 |

| CPU 指令         | 执行                    | 执行         | 停止          | 停止       |                 |

| T0 定时器         | *有效                   | *有效        | *有效         | 无效       | *T0ENB = 1 时有效  |

| TC0 定时器        | *有效                   | *有效        | *有效         | 无效       | *TC0ENB = 1 时有效 |

| TC1 定时器        | *有效                   | *有效        | *有效         |          | *TC1ENB = 1 时有效 |

| <b>丢</b> 门狗皇时哭 | 由 Watch_Dog<br>编译选项控制 |            |             |          | 请参阅编译选项章节       |

| 有门侧足的箱         | 编译选项控制                | 编译选项控制     | 编译选项控制      | 编译选项控制   | 用多购编件起频早日       |

| 内部中断           | 全部有效                  | 全部有效       | T0          | 全部无效     |                 |

| 外部中断           | 全部有效                  | 全部有效       | 全部有效        | 全部无效     |                 |

| 唤醒功能           | -                     | -          | P0,P1,T0,复位 | P0,P1,复位 |                 |

- EHOSC:外部高速时钟。

- ILRC: 内部低速时钟(RC 振荡器: 3V 时 16K, 5V 时 32K)。

# 5.2 系统模式切换

▶ 例:系统由普通/低速模式切换到睡眠模式。

BOBSET FCPUM0 ; CPUM0 = 1.

\* 注:系统进入睡眠模式后,只有具有唤醒功能的引脚和复位引脚能够将系统唤醒并回到普通模式中。

》 例: 系统由普通模式转换到低速模式。

BOBSET FCLKMD

BOBSET FSTPHX ; 外部高速振荡器停振。

例:低速模式转换到普通模式(外部高速振荡器始终处于工作状态)。

B0BCLR FCLKMD

》 例:系统由低速模式转换到普通模式(外部高速振荡器停止工作)。

在外部高速时钟停振的情况下,系统回到普通模式时至少需要延迟 20ms 以稳定振荡器。

BOBCLR FSTPHX : 启动外部振荡器。

B0MOV Z, #54 ; 若 VDD=5V. 内部 RC=32KHz 系统延迟 0.125msX162 = 20.25ms.

@@: DECMS Z JMP @B

BOBCLR FCLKMD : 系统回到普通模式。

》 例:系统由普通模式/低速模式进入绿色模式。

B0BSET FCPUM1

☀ 注:绿色模式下如果禁止 T0 的唤醒功能,则只有具有唤醒功能的引脚和复位引脚可以将系统唤醒(具有唤醒功能的引脚将系统返 回到上一个工作模式,复位引脚将系统返回到普通模式)。

▶ 例:系统由普通/低速模式进入绿色模式,并使能 T0 唤醒功能。

;设置 T0 定时器的唤醒功能。

B0BCLR FT0IEN ; 禁止 T0 中断。 B0BCLR FT0ENB ; 关闭 T0 定时器。 MOV A.#20H :

BOMOV A,#20日 , BOMOV TOM,A ; TO 时钟=Fcpu / 64。

MOV A.#64H

BOMOV TOC,A ; TOC 初始值= 64H (TO 中断间隔= 10 ms)。

BOBCLR FTOIEN ; 禁止 TO 中断。

BOBCLR FTOIRQ ; TO 中断请求寄存器清零。

BOBSET FTOENB ; 开启 TO。

; 进入绿色模式。

BOBCLR FCPUM0 BOBSET FCPUM1

☀ 注:绿色模式下如果使能 T0 的唤醒功能,则具有唤醒功能的引脚、复位引脚和 T0 都能够将系统唤醒。T0 的唤醒周期可编程控 制,请注意对 T0ENB 的设置。

# 5.3 系统唤醒

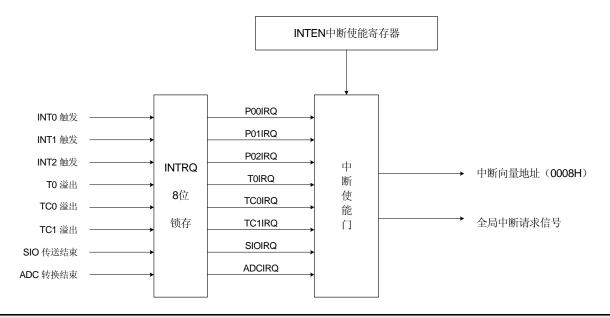

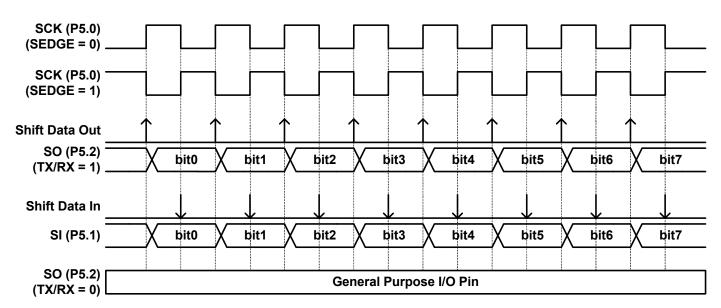

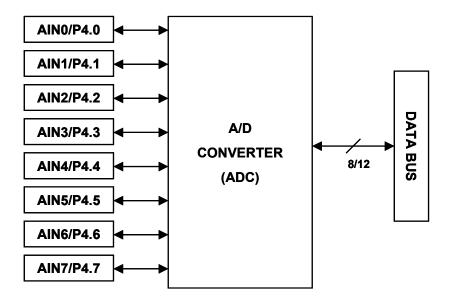

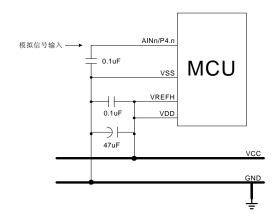

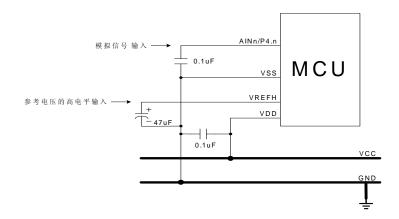

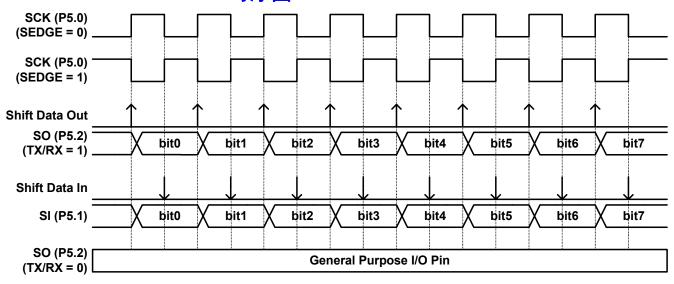

#### 5.3.1 概述